# Principles of Shunt Capacitor Bank Application and Protection

Satish Samineni, Casper Labuschagne, and Jeff Pope *Schweitzer Engineering Laboratories, Inc.*

Presented at the

64th Annual Georgia Tech Protective Relaying Conference

Atlanta, Georgia

May 5–7, 2010

Previously presented at the 63rd Annual Conference for Protective Relay Engineers, March 2010, and 9th Annual Clemson University Power Systems Conference, March 2010

Originally presented at the 36th Annual Western Protective Relay Conference, October 2009

#### 1

# Principles of Shunt Capacitor Bank Application and Protection

Satish Samineni, Casper Labuschagne, and Jeff Pope, Schweitzer Engineering Laboratories, Inc.

Abstract—Shunt capacitor banks (SCBs) are used in the electrical industry for power factor correction and voltage support. Over the years, the purpose of SCBs has not changed, but as new dielectric materials came to market, the fusing practices for these banks changed from externally fused to internally fused, fuseless, and finally to unfused [1]. This paper gives a brief overview of the four most common types of SCBs. What are the differences between them? Which is the best one to use? What type of protection is best suited for each bank configuration?

The paper provides a quick and simple way to calculate the out-of-balance voltages (voltage protection) or current (current protection) resulting from failed capacitor units or elements. While the identification of faulty capacitor units is easy with an externally fused bank, it is more complex with the other types of fusing, making maintenance and fault investigation difficult. This paper presents a novel method to identify the faulted phase and section in capacitor banks.

#### I. INTRODUCTION

SCBs mean different things to different people. From the system operator's viewpoint, an SCB is a system tool that provides voltage support, power factor correction, and/or harmonic filtering. To use this tool, the protection and control scheme must provide the information and the means to control the SCBs. From a designer's viewpoint, an SCB provides a challenge to find the optimum balance of system requirements, cost, maintenance, and spares. From a protection engineer's viewpoint, the protection must cover all faults internal and external to the SCB, and it must be immune to transients, fast, sensitive, and dependable.

This paper provides information for both the design engineer and the protection engineer by giving an overview of bank fusing and grounding, and the more common protection used for these applications. It also shows a simple way to calculate current and voltage out of balance for use during commissioning or setting calculations. The final section of the paper shows a novel method that identifies the phase and section with the faulty unit/element in a shunt capacitor bank.

# II. SHUNT CAPACITOR BANKS

Fusing and protection are the two aspects that determine the optimum bank configuration for a given capacitor voltage rating.

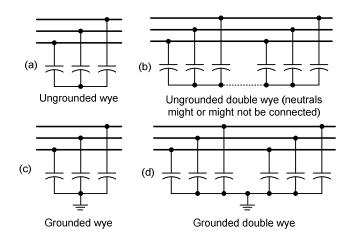

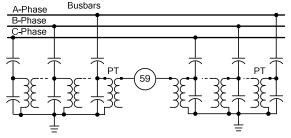

Fig. 1 shows the four most common wye-connected capacitor bank configurations [1]:

Fig. 1. Four most common capacitor bank configurations

#### A. Grounded/Ungrounded Wye

Most distribution and transmission-level capacitor banks are wye connected, either grounded or ungrounded. Characteristics of a grounded bank are as follows:

- Provides a low impedance to ground for lightning surge currents

- Provides a degree of protection from surge voltages

- Reduces recovery voltages for switching equipment (approximately twice normal peak voltage)

- Provides a low impedance to ground for triplen and other harmonic currents

Characteristics of an ungrounded bank are as follows:

- Does not provide a path for zero-sequence currents, triplen, and other harmonic currents

- Does not provide a path for capacitor discharge currents during system faults

- Requires the neutral to be insulated to full line voltage

# III. GENERAL UNIT CAPABILITIES AND CONSTRUCTION

IEEE Std C37.99-2000 [1] defines a number of operating criteria for capacitor units. From a fusing viewpoint, the following two requirements are important:

- Abnormal operating conditions must be limited to 110 percent of rated root-mean-square (RMS) terminal voltage

- The capacitor should be able to carry 135 percent of nominal RMS current

Capacitor banks are constructed by the series/parallel combination of capacitor units. Units are connected in parallel (parallel groups) to meet the VAR specification of the

capacitor bank. These parallel groups are then connected in series to meet the nameplate voltage rating of the capacitor units. Capacitor units are available over a wide voltage range (216 V to 24,940 V), and VAR ratings (2.5 kVAR to around 800 kVAR [1]).

With this wide range of VAR and voltage ratings, the bank designer must find a good compromise between cost (number of units in the bank, the complexity of the bank construction, maintenance and spares) and the impact of an element/unit failure. For example, when a fuse blows in an externally fused bank, one whole unit is disconnected. If the bank used only a few units of large kVAR rating, a significant amount of kVAR could be lost. Depending on the function of the bank, a large kVAR (capacitance) loss impacts the amount of available voltage support, the degree of power factor correction, or the effectiveness of the filtering (filter banks).

# IV. TO FUSE OR NOT TO FUSE?

Although many factors influence the design of a capacitor bank, developments in the dielectric play a major role in determining the character of element failures within a unit.

Earlier capacitor units used kraft paper with a PCB impregnant as dielectric. Although the kraft paper was highly refined, there were still many non-uniformities in the paper [2]. To avoid weak spots in the dielectric, capacitor units had several layers of paper inserted between the foil layers. When dielectric material of this type failed, the foil layers did not weld together to form a solid connection. Instead, the cellulose continued to arc, resulting in charring of the paper that generated gas inside the sealed capacitor unit. In many cases, this gas buildup caused the unit to rupture, resulting in damage beyond the failure of a single element.

Present-day dielectrics are manufactured with as few as two to three layers of impregnated polypropolene film (as opposed to many layers of kraft paper). Because the film layers are thin, failures now cause the foils to weld together, thus forming a solid connection between the foils without arcing or charring.

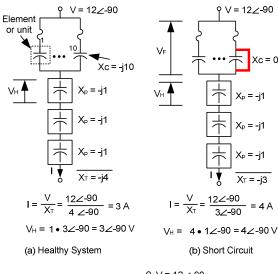

To visualize the three stages of a fuse blowing, consider the arrangement in Fig. 2. This arrangement shows four series groups of 10 capacitors in parallel, with an applied voltage of 12 V. A capacitor symbol represents either one row of an internally fused unit or a complete unit in an externally fused bank.

Fig. 2. Three stages of a fuse blowing

The labels in Fig. 2 are as follows.

$X_C$  = The reactance of each element/unit (10  $\Omega$ )

$X_P$  = Reactance of a parallel group of elements/units

$X_T$  = Total reactance of the circuit

VF = Voltage across the faulted parallel group of elements/units

VH = Voltage across the healthy parallel group of elements/units

In Fig. 2(a), the system is healthy and the voltage across each of the four series groups is 3 V. Fig. 2(b) depicts the circuit just after a short circuit occurs, but before the fuse blows (fused application). In a fuseless bank, Fig. 2(b) shows the final state. In this state, the following circuit conditions prevail:

- All the elements/units in parallel with the faulted element/unit are shorted out

- The total reactance decreases

- The total current increases

- The voltage across the healthy series elements/units increases

- The increased voltage is evenly distributed among the healthy series elements/units

Fig. 2(c) depicts the circuit after the fuse blew. At this time, the following circuit conditions prevail:

- The reactance of the faulted parallel group increases

- The voltage across all the elements/units in the faulted parallel group increases

- The total reactance increases

- The total current decreases

- The voltage across the healthy elements/units decreases

- The decreased voltage is evenly distributed among the healthy elements/units

When a capacitor element fails, there is an increase in current through the fuse of the failed element. This current consists of two components:

- Increase in fundamental frequency current resulting from the decrease in reactance

- Increase in transient current, resulting from the discharge from the healthy parallel elements

Both components must be considered when selecting a fuse size: the fuse on the healthy elements must not blow when discharging into an adjacent faulted capacitor, but must quickly and effectively remove a failed element/unit.

#### a) Externally Fused Units

Units in an externally fused bank have a few elements in parallel but many elements in series [2]. When an element fails (welds together), the entire row of elements shorts out (Fig. 2[b]). With only a few elements in parallel, the capacitance lost is small, and with many elements in series, the increase in voltage across the healthy series units is also small. Units can be designed for a relatively high voltage, because the external fuse can interrupt a high-voltage fault.

# (1) Impact on Bank Design

Carefully consider the series/parallel combinations of the units when constructing an externally fused bank, particularly regarding voltage and kVAR ratings. Selecting units with the highest available voltage rating results in the fewest series groups and also provides the greatest sensitivity for unbalance protection. Selecting larger kVAR ratings means fewer units (for the same VAR requirement), but increases the voltage across the healthy parallel units following a fuse blowing. Because of this high voltage stress, subsequent failures in the same parallel group are likely to occur.

Select the minimum number of units in parallel greater than 10 to ensure that one open fuse does not leave more than 10 percent overvoltage on the remaining units in that parallel group [3] [4]. Select the maximum number of units in parallel such that the total energy a parallel group stores is less than 15 kJ (all-film dielectric) or 10 kJ (all-paper or paper-film dielectric) at peak maximum voltage.

#### b) Internally Fused Units

Internally fused units are manufactured with many elements in parallel [2]. When an element fails (welds together), the fuse of the faulty elements blows, disconnecting the faulty element from the other parallel elements (Fig. 2[c]). With many elements in parallel, lost capacitance is small and the increase in voltage across the healthy parallel units is also small. Because of the large number of parallel elements in this

unit, many elements can fail before unbalance tripping is necessary.

# (1) Impact on Bank Design

To construct a bank with the fewest number of units, select units with the highest available kVAR rating. The minimum number of units in parallel should be two units; the maximum number of units in parallel depends on the value of discharge current from the parallel units. Select this value according to the capacitor manufacturer's recommendation.

#### c) Fuseless Banks

Based on modern-day high-quality dielectrics, fuseless units are similar in construction to externally fused units (few elements in parallel, but many elements in series). When an element fails (welds together), the entire row of elements shorts out (Fig. 2[b]). However, unlike the fused installations, there are now no fuses to blow, and the effect of a failed element on the bank is permanent. Because there are no fuses in this bank, we can visualize the bank in terms of elements rather than units.

# (1) Impact on Bank Design

Fuseless banks are constructed with at least 10 elements in series to ensure that when an element fails, the remaining series elements do not exceed the 110 percent overvoltage requirement. For example, if there are 10 capacitor units in series, and each unit has 10 elements (total 100 elements in series), then the increase across the remaining series elements is 100/99 or approximately 1 percent (see Fig. 2[b]). The higher the voltage of the bank, the more capacitor elements must be connected in series.

# d) Unfused Banks

Unfused banks are constructed with elements in a series/parallel combination. These units are similar to fuseless units, i.e., when an element fails (welds together), the entire row of elements is shorted out (Fig. 2[b]).

# (1) Impact on Bank Design

For unfused banks, the general overvoltage requirement applies, i.e., the voltage on the healthy elements/units must not exceed 110 percent of their rating (or the recommended rating that the manufacturer specifies).

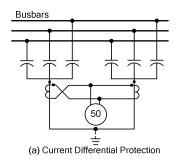

# V. UNBALANCE PROTECTION METHODS

Unbalance protection provides protection against faults within an SCB. For this protection, we use either voltage or current measuring methods. The particular protection depends on the fusing method (externally fused banks use the fuse as the first line of protection), the size of the bank, the method of grounding, and the required insulation of the CT/PT [5]. Following are examples of the more common unbalance protection methods.

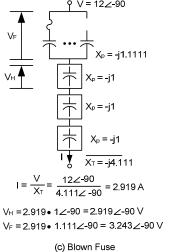

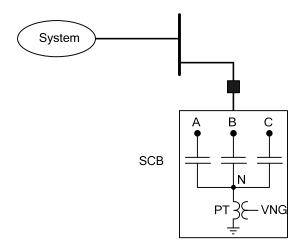

# A. Unbalance Protection for Ungrounded, Single-Wye Banks

The simplest method for this application is to measure the bank zero-sequence voltage [1]. The voltage-sensing device can be a voltage transformer, capacitive potential device, or resistive potential device. Fig. 3 shows three methods to measure the zero-sequence voltage. Fig. 3(a) shows a brokendelta connection to measure 3V0, Fig. 3(b) shows a PT

between the bank neutral and ground to measure V0, and Fig. 3(c) shows a compensated neutral unbalance method. Unlike the first two methods, the compensated neutral unbalance method removes the system unbalance.

Fig. 3. Unbalance protection for ungrounded, single-wye banks

# B. Unbalance Protection for Ungrounded, Double-Wye Banks

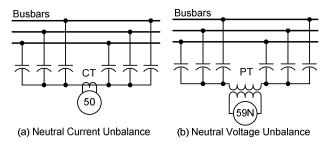

Splitting the bank into two equal wye sections and measuring the neutral current (Fig. 4[a]) or voltage (Fig. 4[b]) provides for protection that is insensitive to system voltage unbalance. The measurement is insensitive to this unbalance because the protection senses the neutral current or voltage differentially, i.e., both wye sections are affected equally by any system voltage unbalance.

Fig. 4. Neutral current and neutral voltage unbalance

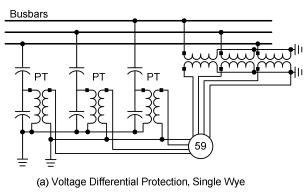

# C. Unbalance Protection for Grounded, Single-Wye Banks

Fig. 5(a) shows unbalance voltage protection using busbar PTs and PTs connected to tap points. Unbalances in the bank change the tap point voltage with respect to the busbar voltage, causing the relay to operate. Fig. 5(b) shows an example of a phase unbalance differential current measurement whereby a CT is connected between two equal strings of the same phase. Notice that this application can be

grounded or ungrounded. When we make the connection between the two strings near the mid-point of the strings, the connection is known as an H-bridge. The protection is insensitive to system unbalances.

(b) Phase Unbalance or H-Bridge

Fig. 5. Unbalance protection for grounded, single-wye banks

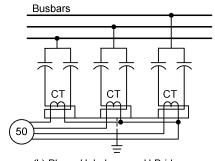

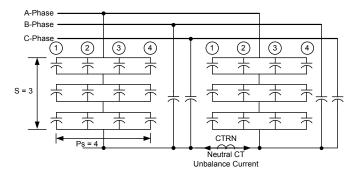

# D. Unbalance Protection for Grounded, Double-Wye Banks

Fig. 6(a) shows unbalance current and Fig. 6(b) shows unbalance voltage protection. In Fig. 6(a), a CT is installed in the neutral of each wye-connected bank and the neutrals connect to ground. The CTs are cross-connected to form a differential measurement, then connected to an overcurrent element. In Fig. 6(b), the protection uses two PTs per phase connected to similar tap positions on the two phases.

(b) Voltage Differential Protection, Double Wye

Fig. 6. Unbalance current and unbalance voltage protection

#### VI. UNBALANCE CALCULATIONS

The calculations we use to determine the effects of failed units, elements, or fuses in a capacitor bank play a key role in the knowledge necessary for the proper application of the protective relay. Calculating equations occur often on an asneeded basis, depending upon capacitor bank configuration, system operating parameters, and the type of protection being applied. Selection of the correct equations, and then verification of the results can be a confusing and time-consuming process.

# A. Unbalance Calculations Using IEEE Standard C37.99-2000

The IEEE Standard C37.99-2000, IEEE Guide For The Protection of Shunt Capacitor Banks, provides one source of possible calculations for determining the voltages and current imbalances created by failures within the capacitor bank. The C37.99 standard provides calculations for internally fused, externally fused, fuseless, and unfused capacitor banks. We separate the calculations into unbalance and tapped applications. Unbalance applications refer to those capacitor banks using phase or neutral differential current, or phase-to-neutral voltage to measure the amount of unbalance in the capacitor bank. Tapped applications refer to a voltage differential application that use a tapped voltage within the capacitor bank to measure the voltage division ratio of the capacitor bank.

The results of the C37.99 standard calculations are in perunit quantities. The determination of the base needed to convert the per-unit values to primary quantities depends on the system and capacitor bank rated voltages, and also the capacitor bank configuration and power ratings. Conversion of the primary quantities into secondary quantities that the relay uses is a matter of applying the correct voltage or current transformation ratios used on the respective input. In the following examples, we calculate the C37.99 perunit quantities and resulting primary quantities and compare these quantities to simulations of various unit, element, or fuse failures within the capacitor bank. The equations, and the simulations, are for failures occurring within the same group or string within the capacitor bank.

# 1) Case 1: Externally Fused Bank With Voltage Tap

In this case, we apply the C37.99 standard equations to an example capacitor bank with the design parameters shown in Table I:

TABLE I

CAPACITOR BANK CONFIGURATION DATA

| Cap Bank Configuration                      | Units    |           |  |

|---------------------------------------------|----------|-----------|--|

| Series Groups (S)                           | 4        |           |  |

| Parallel Units per Phase (Pt)               | 6        |           |  |

| Grounding                                   | Grounded |           |  |

| Rated Capacitor Bank Voltage (kV line-line) | 139.00   | $kV_{LL}$ |  |

| Nominal System Voltage (kV line-line)       | 125.00   | $kV_{LL}$ |  |

| Rated Cap Bank Power (KVAR)                 | 27000.00 | kVAR      |  |

| PT Ratio Bus                                | 695.00   |           |  |

| PT Ratio Tap/Neutral                        | 232.00   |           |  |

| Series Groups Within Tap Portion (St)       | 2        |           |  |

Using the IEEE C37.99 per-unit system for the initial calculations, the following results were converted to primary and secondary voltage, as shown in Table II.

These results were then compared with a simulation of a mathematical model that used the same system and capacitor bank values, as shown in Table III.

TABLE II

PRIMARY AND SECONDARY VOLTAGES CALCULATED USING IEEE C37.99 EQUATIONS

| Number of<br>Faulted<br>Units | Tap Primary<br>Voltage (V) Fault<br>Above Tap | Tap Primary<br>Voltage (V) Fault<br>Below Tap | Tap Voltage—Fault<br>Above Tap, Secondary<br>Voltage (V) | Tap Voltage—Fault<br>Below Tap Secondary<br>Voltage | Voltage On Affected<br>Capacitor Group (kV) |

|-------------------------------|-----------------------------------------------|-----------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|---------------------------------------------|

| 0                             | 36084.392                                     | 36084.392                                     | 155.536                                                  | 155.536                                             | 18.042                                      |

| 1                             | 34366.087                                     | 37802.696                                     | 148.130                                                  | 163.943                                             | 20.620                                      |

| 2                             | 32075.015                                     | 40093.769                                     | 138.254                                                  | 172.818                                             | 24.056                                      |

| 3                             | 28867.513                                     | 43301.270                                     | 124.429                                                  | 186.643                                             | 28.868                                      |

| 4                             | 24056.261                                     | 48112.522                                     | 103.691                                                  | 207.382                                             | 36.084                                      |

| 5                             | 16037.507                                     | 56131.276                                     | 69.127                                                   | 241.945                                             | 48.113                                      |

TABLE III

CALCULATED VS. SIMULATED DATA MEASUREMENT AND ERROR

| Number of<br>Faulty<br>Units | Calculated Tap<br>Primary Voltage<br>Fault Above Tap | Simulated Tap<br>Primary Voltage<br>Fault Above Tap | Error (%) | Calculated Tap<br>Primary Voltage Fault<br>Below Tap | Simulated Tap<br>Primary Voltage<br>Fault Below Tap | Error (%) |

|------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------|------------------------------------------------------|-----------------------------------------------------|-----------|

| 0                            | 36084.39                                             | 36097.80                                            | -0.04%    | 36084.39                                             | 36080.80                                            | 0.01%     |

| 1                            | 34366.09                                             | 34358.80                                            | 0.02%     | 37802.70                                             | 37799.10                                            | 0.01%     |

| 2                            | 32075.02                                             | 32067.80                                            | 0.02%     | 40093.77                                             | 40090.20                                            | 0.01%     |

| 3                            | 28867.51                                             | 28860.60                                            | 0.02%     | 43301.27                                             | 43297.80                                            | 0.01%     |

| 4                            | 24056.26                                             | 24049.90                                            | 0.03%     | 48112.52                                             | 48109.30                                            | 0.01%     |

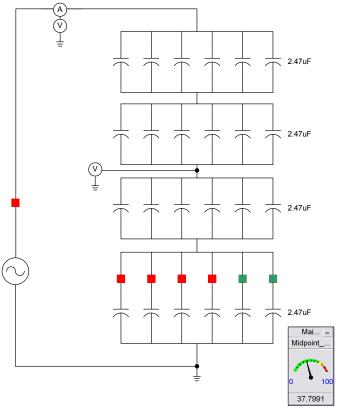

Fig. 7 shows the simulation software representation of Case 1.

Fig. 7. Externally fused, tapped simulation example for fault below tap point

In this case, we calculate all secondary quantities by multiplying the per-unit values provided by the IEEE C37.99 standard by the system line-to-neutral voltages.

# 2) Case 2: Internally Fused with Current or Voltage Imbalance

The second case presented is of an internally fused capacitor bank with the configuration shown in Fig. 4. Table IV shows the resulting currents and voltages under healthy conditions and with up to six blown fuses in Table V.

TABLE IV

INTERNALLY FUSED CAPACITOR BANK CONFIGURATION

| Cap Bank Configuration                                    | Cap Bank Configuration Units |           |  |  |

|-----------------------------------------------------------|------------------------------|-----------|--|--|

| Series Groups (S)                                         | 3                            |           |  |  |

| Parallel Units Per Phase (Pt)                             | 6                            |           |  |  |

| Parallel Units Per Phase in Left Wye (Pa)                 | 3                            |           |  |  |

| Parallel Elements Per Group (N)                           | 7                            |           |  |  |

| Number of Series Element Groups in Capacitor<br>Unit (Su) | 4                            |           |  |  |

| Grounded Cap Bank (0 = Grounded,<br>1 = Ungrounded)       | 1                            |           |  |  |

| Rated Capacitor Bank Voltage (kV line-line)               | 139.00                       | $kV_{LL}$ |  |  |

| Nominal System Voltage (kV line-line)                     | 125.00                       | $kV_{LL}$ |  |  |

| Rated Cap Bank Power (KVAR)                               | 28000.00                     | kVAR      |  |  |

| Current Imbalance CT Ratio                                | 3.20                         |           |  |  |

| PT Ratio Bus                                              | 695.00                       |           |  |  |

| PT Ratio Tap/Neutral                                      | 232.00                       |           |  |  |

TABLE V

CALCULATED VALUES FOR INTERNALLY FUSED SCB

| Number of Faulty<br>Units/Elements/<br>Fuses | Primary Neutral<br>to Ground<br>Voltage | Secondary Neutral<br>to Ground Voltage | Voltage on<br>Affected Unit (kV<br>L-N) | Primary Neutral<br>Current Between<br>WYEs | Primary Difference<br>Current, Equal<br>WYES |

|----------------------------------------------|-----------------------------------------|----------------------------------------|-----------------------------------------|--------------------------------------------|----------------------------------------------|

| 0                                            | 0.00                                    | 0.00                                   | 24056.26                                | 0.00                                       | 0.00                                         |

| 1                                            | 53.98                                   | 0.23                                   | 24290.17                                | 0.12                                       | 0.12                                         |

| 2                                            | 124.21                                  | 0.54                                   | 24594.53                                | 0.27                                       | 0.27                                         |

| 3                                            | 219.36                                  | 0.95                                   | 25006.81                                | 0.48                                       | 0.48                                         |

| 4                                            | 355.51                                  | 1.53                                   | 25596.81                                | 0.77                                       | 0.77                                         |

| 5                                            | 566.47                                  | 2.44                                   | 26510.98                                | 1.23                                       | 1.23                                         |

| 6                                            | 937.26                                  | 4.04                                   | 28117.71                                | 2.04                                       | 2.04                                         |

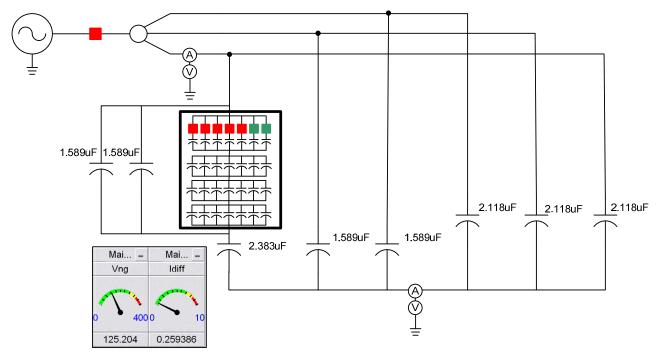

Fig. 8 shows the simulation software representation of Case 2.

Fig. 8. Simulation of the internal capacitor bank

Table VI shows the results of the calculated values as compared to the values from the simulations.

TABLE VI

CALCULATED VS. SIMULATED MEASUREMENT AND ERROR

| Number<br>of Faulty<br>Units | Calculated<br>Primary<br>Neutral to<br>Ground<br>Voltage<br>(87VN) | Simulated<br>Primary<br>Neutral to<br>Ground<br>Voltage | Error  | Calculated<br>Voltage on<br>Affected<br>Unit (V) | Simulated<br>Voltage on<br>Affected<br>Unit | Error  | Calculated<br>Primary<br>Neutral<br>Current<br>Between WYEs | Simulated<br>Primary<br>Neutral<br>Current<br>Between WYEs | Error<br>(%) |

|------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|--------|--------------------------------------------------|---------------------------------------------|--------|-------------------------------------------------------------|------------------------------------------------------------|--------------|

| 0                            | 0.00                                                               | 0.00                                                    | 0.00%  | 24056.26                                         | 24195.00                                    | -0.58% | 0.00                                                        | 0                                                          | 0.00%        |

| 1                            | 53.98                                                              | 54.56                                                   | -1.07% | 24290.17                                         | 24430.20                                    | -0.58% | 0.12                                                        | 0.113                                                      | 5.83%        |

| 2                            | 124.21                                                             | 125.20                                                  | -0.80% | 24594.53                                         | 24936.40                                    | -1.39% | 0.27                                                        | 0.2594                                                     | 3.93%        |

| 3                            | 219.36                                                             | 220.90                                                  | -0.70% | 25006.81                                         | 25151.00                                    | -0.58% | 0.48                                                        | 0.4576                                                     | 4.67%        |

| 4                            | 355.51                                                             | 357.84                                                  | -0.65% | 25596.81                                         | 25744.50                                    | -0.58% | 0.77                                                        | 0.74132                                                    | 3.72%        |

| 5                            | 566.47                                                             | 570.02                                                  | -0.63% | 26510.98                                         | 26663.90                                    | -0.58% | 1.23                                                        | 1.181                                                      | 3.98%        |

| 6                            | 937.26                                                             | 942.94                                                  | -0.61% | 28117.71                                         | 28279.90                                    | -0.58% | 2.04                                                        | 1.953                                                      | 4.26%        |

The error shown for the simulated primary neutral current between wyes is largely due to the small signal generated by the model, as well as errors generated by the individual capacitive elements within the model.

Note in Table V that the Primary Neutral Current between Wyes and the calculated Primary Difference Current, Equal Wyes is identical. This is because this capacitor bank configuration has half of the parallel units per phase (Pt) on each side of the neutral CT.

The conversion from per-unit to secondary quantities displayed in Table V was according to the following base quantities:

- Voltage Neutral to Ground: Vng System L-N

Voltage (Vng is the IEEE C37.99 per-unit quantity)

- Voltage on Affected Unit: Vcu Unit Nominal Voltage (Vcu is the IEEE C37.99 per-unit quantity, and Unit Nominal Voltage is the voltage across the capacitor unit under normal operating conditions)

- Neutral Current Between WYEs: In Iph (In is the IEEE C37.99 per-unit quantity, and Iph is the phase current at nominal system voltage).

- Difference Current, Equal WYEs: Id Iph (Id is the IEEE C37.99 per-unit quantity, and Iph is the phase current at nominal system voltage).

In general, the calculations from the IEEE C37.99 standard provide a reliable method for predicting per-unit values of voltage and current unbalance with a variable number of failures within the capacitor bank. The simulations support the methods used to convert from primary to secondary quantities.

# B. Unbalance Calculations Using Millman's Theorem

The calculations in IEEE C37.99 can be difficult to interpret if one must understand the underlying calculations leading to the condensed equations shown in the guide. Another method for calculating voltage and current imbalance quantities for capacitor banks is more intuitive. This method uses the conversion from capacitor unit capacitance to reactive impedance (Xc), and uses Millman's theorem for calculating the neutral-to-ground voltage on the affected string.

Millman's Theorem states that: "If any number of admittances  $Y_1, Y_2, Y_3, ... Y_n$  meet at a common point P, and the voltages from another point N to the free ends of these admittances are  $E_1, E_2, E_3, ... E_n$  then the voltage between points P and N is:" [6]

$$V_{PN} = \frac{\sum E_n \cdot Y_n}{\sum Y_n}$$

(1)

Millman's theorem requires that we condense the capacitor bank down to three equivalent admittances, where two of the three values represent the unaffected healthy phases of the capacitor bank, and the third represents the phase with the faulted units. For example, for the externally fused capacitor bank in Fig. 9, and the capacitor bank configuration values in Table VII, the general equations are as follows:

S = series groups, line to neutral

Ps = parallel units per phase

Pt = total parallel units per phase, 4 + 4 =8

Fig. 9. Externally fused capacitor bank with two parallel strings per phase

TABLE VII

EXTERNALLY FUSED CAPACITOR BANK CONFIGURATION

| Prompt                                             | Range   | Default | Variable          |

|----------------------------------------------------|---------|---------|-------------------|

| System Frequency (50, 60)                          | 50, 60  | 60      | <nfreq></nfreq>   |

| Total Number Parallel Units in One<br>Group (1–99) | 1–99    | 4       | <ps></ps>         |

| Number of Series Groups Line to<br>Neutral (1–99)  | 1–99    | 3       | <s></s>           |

| Line-to-Line Voltage in kV (1–99999 kV)            | 1–99999 | 88      | <kvll></kvll>     |

| Capacitance of Capacitor Unit in uF (1–999 uF)     | 1–999   | 20      | <capval></capval> |

| Neutral CT Ratio (1–99999)                         | 1–99999 | 2       | <ctrn></ctrn>     |

| Number of Blown Fuses (0–99)                       | 0–99    | 0       | <n></n>           |

$Pt = 2 \cdot Ps$ . Note that this capacitor bank example uses two parallel strings with equal numbers of capacitor units in each group.

Use (2) to convert from capacitance to reactance.

$$Xc = \frac{1 \cdot 10^6}{2 \cdot \pi \cdot NFREQ \cdot CAPVAL}$$

(2)

Reduce the capacitor bank to that shown in Fig. 9 by paralleling the two B-phase strings into a single B-phase string. Do the same with the C-phase. For this calculation, the faulted capacitor unit will be (arbitrarily) in the A-phase. Therefore, keep the two A-phase phases separate: one will be healthy, the other will be faulted.

Use (3) to calculate the total reactance of a healthy group (combined wyes), healthy phases.

$$Xgh = \frac{Xc}{Pt}$$

(3)

Use (4) to calculate the reactance of a healthy group, faulty phase (A-phase).

$$XghA = \frac{Xc}{P_S}$$

(4)

Use (5) to calculate the reactance of the faulty group, faulty phase (A-phase).

$$XgfA = \frac{Xc}{P_{S-n}}$$

(5)

Use (6) to calculate the total reactance of the healthy phase(s).

$$Xphh = S \cdot Xgh \tag{6}$$

Use (7) to calculate the total reactance of the faulty leg.

$$XlegfA = (S - 1) \cdot XghA + XgfA \tag{7}$$

Use (8) to calculate the total reactance of the healthy leg, faulty phase.

$$XleghA = S \cdot XghA \tag{8}$$

Use (9) to calculate the reactance of the healthy group, faulty phase (A-phase).

$$Xphf = \frac{Xlegfa \cdot Xlegha}{Xlegfa + XleghA}$$

(9)

This completes the calculations for the various reactances. Applying Millman's Theorem, the neutral-to-ground voltage, VNG, is as follows:

$$VNG = \frac{VA \cdot YA + VB \cdot YB + VC \cdot YC}{YA + YB + YC}$$

(10)

Use (11) to calculate VNG, the neutral voltage in primary volts, using Millman's Theorem.

$$VNG = \frac{\frac{KVLL \cdot 1000 \cdot e^{j0^{\circ}}}{\sqrt{3} \cdot Xphf} + \frac{KVLL \cdot 1000 \cdot e^{j-120^{\circ}}}{\sqrt{3} \cdot Xphh} + \frac{KVLL \cdot 1000 \cdot e^{j120^{\circ}}}{\sqrt{3} \cdot Xphh}}{\frac{1}{Xphf} + \frac{2}{Xphh}}$$

(11)

Use (12) to calculate VNG in secondary volts

$$VNGsec = \frac{|VNG|}{PTRN}$$

(12)

Once we know the neutral-to-ground voltage, we can calculate the difference current by dividing the VNG value by the Thevenin equivalent reactance for the faulty capacitor bank string.

$$60N = \frac{|VNG|}{Xth}$$

(13)

Calculation and simulation of capacitor bank failures has shown that using either the IEEE C37.99 standard equations or the equations that use capacitor bank impedances and Millman's Theorem provide satisfactory results for calculating the effects of failures on unbalance currents and voltages within a wide variety of capacitor banks.

# VII. FAULTED PHASE AND SECTION IDENTIFICATION (PATENT PENDING)

SCBs play a critical role in providing local reactive power support and thereby regulating the voltage. It is very important that SCB outages be as short as possible. Part of the outage time is spent identifying the faulty unit. Identifying the faulty units in an SCB helps return the bank to service in a minimum time. If the SCB is externally fused, then the unit with the blown fuse is usually the faulty unit, making the identification obvious. If the SCB is internally fused, fuseless, or unfused, then fault identification is very difficult because there is no visual indication of the faulted element. The result is an extended outage. Although it might not be possible to identify the faulty unit in internally fused, fuseless, or unfused bank, identifying the faulted phase helps minimize the outage time.

To identify the faulted phase, we propose a novel method based on phase relationship between quantities measured by the protective relay.

For grounded SCBs with tapped voltage differential protection, the faulted phase is the phase for which the protection has operated. Furthermore, we can identify the faulted section (top or bottom from the tapped point) based on the differential voltage dVp [5] polarity (where p = A, B, C). If the differential voltage dVp is less than or equal to zero and SCB has no fuses, then the faulty unit is on phase p and in the top section from the tap point. If the differential voltage dVp is greater than zero, the faulty unit is on phase p and in the bottom section from the tap point. If the SCB has fuses, then section identification is opposite (if dVp is less than or equal to zero, then the faulty unit is in the bottom section, and if dVp is greater than zero, the faulty unit is in the top section).

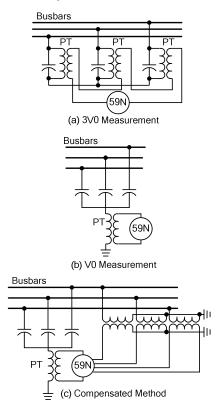

For ungrounded SCBs with voltage unbalance or current unbalance protection, identifying the faulted phase is not obvious because the protection is based on neutral voltage or current (a quantity derived from all three phases).

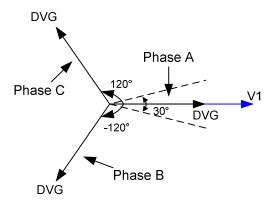

For a single-wye, ungrounded SCB, as shown in Fig. 10, the protection we use is neutral voltage unbalance protection. We measure the neutral point voltage (VNG) which includes the system unbalance as well as the SCB unbalance. We also measure the zero-sequence voltage at the bus (3V0). The difference between the two voltages gives the unbalance in the SCB. If we correct the difference both in phase and magnitude, then the difference (for example, difference voltage DVG) is zero for normal conditions.

Fig. 10. Single-wye ungrounded SCB

Consider an SCB that is not fused. A fault develops in a unit in the A-phase, resulting in a difference voltage, DVG. For this fault, the phase angle of the difference voltage and the phase angle of the positive-sequence voltage (V1) are in phase. If the faulty unit is in the B-phase, then the phase angle of DVG lags the phase angle of V1 by 120 degrees. Similarly, if the fault is on C-phase, the phase angle of DVG leads the phase angle of V1 by 120 degrees. Using the phase relationship between DVG and V1, we can identify the phase with the faulty units.

For security, we need to apply  $\pm 15$  degree blinder for unbalances not resulting from capacitor failures. For sensitivity, we can either use the trip (or alarm) condition for supervising the phase identification.

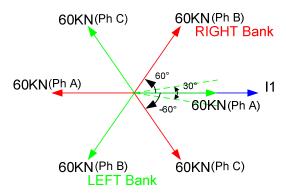

Fig. 11 shows the phase relationship between DVG and V1 for faulty units in different phases in an SCB without fuses.

Fig. 11. Phase relationship between difference voltage DVG and positive-sequence voltage V1 for faulty units in different phases in a SCB with no fuses

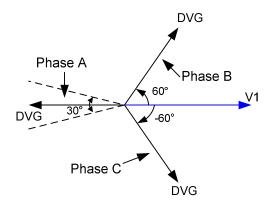

If the SCB has fuses, then the phase relationship will be 180 degrees out-of-phase compared to an SCB with fuses. Fig. 12 shows the phase relationship between DVG and V1 for faulty units in different phases in a SCB with fuses.

Fig. 12. Phase relationship between difference voltage DVG and positivesequence voltage V1 for faulty units in different phases in a SCB with fuses

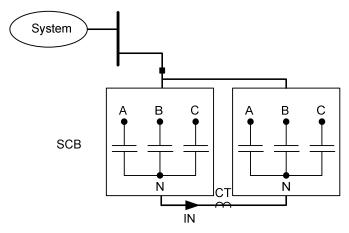

Consider the double-wye, ungrounded SCB in Fig. 13. For this application, we use neutral current unbalance protection, measuring the neutral current (IN) that is the capacitor bank unbalance. We reference the measured neutral current with the positive-sequence current (I1) drawn by the two banks. If we correct the measured neutral current both in phase and magnitude, then the unbalance (for example, unbalance current [60KN]) is zero for normal conditions.

Fig. 13. Double-wye ungrounded SCB

Consider an SCB with no fuses that develops a fault in a unit in Phase A of the left bank. This fault causes unbalance current to flow in the neutral. This unbalance current will be in phase (or 180 degrees out of phase, according to the polarity of the neutral CT) with I1. If the faulty unit is in Phase A of the right bank, then 60KN will be 180 degrees out of phase with I1. If the faulty unit is in Phase B of the left bank, then 60KN lags I1 by 120 degrees. If the faulty unit is in Phase B of the right bank, then the unbalance current leads I1 by 60 degrees. If the faulty unit is in Phase C of the left bank, then 60KN leads I1 by 120 degrees. If the faulty unit is in Phase C of the right bank, then 60KN lags I1 by 60 degrees.

Using the 60KN and I1 phase relationship, we can identify both the phase with the faulty unit and the faulty section of the bank (left or right).

For security we need to apply a  $\pm 15^{\circ}$  blinder for unbalances not resulting from capacitor failures. For

sensitivity, we can either use the trip (or alarm) condition for supervising the phase identification.

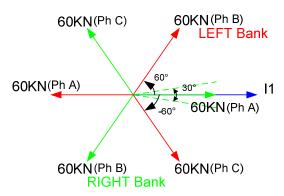

Fig. 14 shows the phase relationship between 60KN and I1 for faults on different phases and on different sections of the SCB with no fuses. Green vectors represent 60KN for faults on the left bank. Red vectors represent 60KN for faults on the right bank (polarity of neutral CT agreeing with Breaker CT).

Fig. 14. Phase relationship between unbalance current 60KN and positivesequence current I1 for faults on different phases and on different sections of the SCB with no fuses

If the SCB has fuses, then the phase relationship will be 180 degrees offset to the SCB without fuses. Fig. 15 shows the phase relationship between 60KN and I1 for faults on different phases and on different sections of the SCB. Green vectors represent 60KN for faults on the right bank. Red vectors represent 60KN for faults on the left bank (polarity of neutral CT agreeing with Breaker CT).

Fig. 15. Phase relationship between unbalance current 60KN and positive sequence current II for faults on different phases and on different sections of the SCB with fuses

To demonstrate the proposed concept, we modeled a power system in the RTDS. The system consists of a source, SCB (five strings per phase) and a load. The source voltage is 230 kV. For the first case, consider an SCB configured as an ungrounded, fuseless, single-wye bank. A potential transformer measures the unbalance voltage between the neutral of the SCB and ground. Each string has 12 units in series and each unit has 6 series connected elements. The capacitance of each element is  $60.8~\mu F$  (courtesy of Terry Fix, Dominion Virginia Power). We simulated a faulty element by shorting an element in the unit.

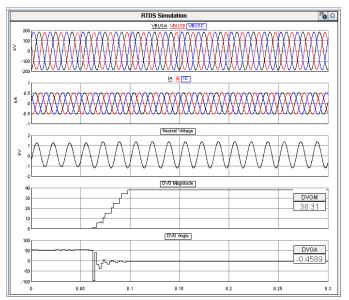

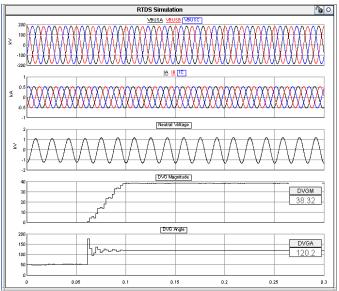

Fig 16 shows the bus voltage, bus current, neutral voltage, difference voltage magnitude (DVGM), and difference voltage angle (DVGA). An element in A-phase of the SCB is shorted, resulting in a difference voltage magnitude of 38 V and a phase angle close to 0 degrees.

Fig. 16. Ungrounded single-wye SCB with a faulty element in A-phase

An element in B-phase of the SCB is shorted, causing a difference voltage of magnitude 38 V and a phase angle close to  $-120^{\circ}$ , as shown in Fig. 17.

Fig. 17. Ungrounded single wye SCB with a faulty element in B-phase

An element in C-phase of the SCB is shorted, causing a difference voltage with magnitude of 38 V and phase angle close to +120 degrees, as shown in Fig. 18.

Fig. 18. Ungrounded single-wye SCB with a faulty element in C-phase

For the second case, an SCB is configured as an ungrounded double-wye bank, with the two neutrals connected. The SCB has five strings per phase on the left bank and four strings per phase on the right bank. A neutral current transformer measures the bank unbalance. Each string has 12 units in series and each unit has 6 series connected elements. The capacitance of each element is 60.8  $\mu F$  (courtesy of Terry Fix, Dominion Virginia Power).

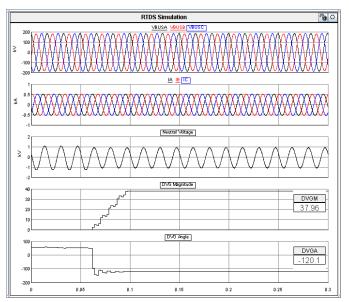

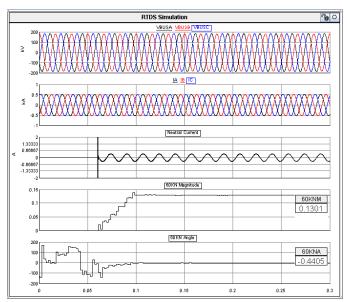

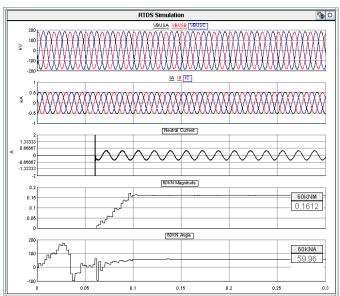

Fig. 19 shows the bus voltage, bus current, neutral current, neutral current magnitude (60KNM), and neutral current angle (60KNA). An element in the A-phase left section of the SCB is shorted, causing an unbalance current magnitude of 130 mA and a phase angle close to 0 degrees.

Fig. 19. Ungrounded double-wye SCB with a faulty element in A-phase of left section

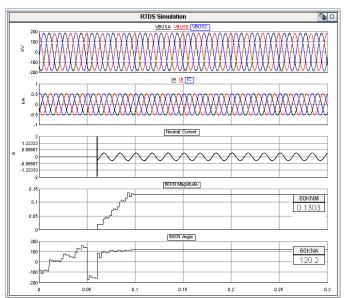

An element in the A-phase, right section of the SCB is shorted, causing an unbalance current magnitude of 163 mA and a phase angle close to 180 degrees, as shown in Fig. 20.

Fig. 20. Ungrounded double-wye SCB with a faulty element in A-phase of right section

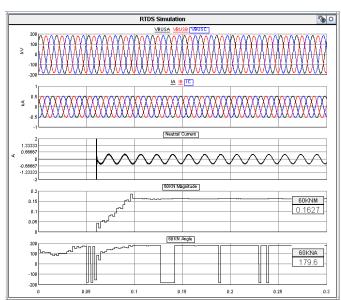

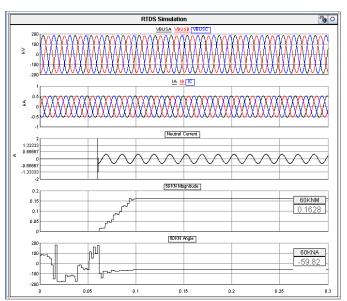

An element in the B phase, Left section of the SCB is shorted, causing an unbalance current magnitude of 129 mA and a phase angle close to -120 degrees, as shown in Fig 21.

Fig. 21. Ungrounded double wye SCB with a faulty element in B-phase of left section

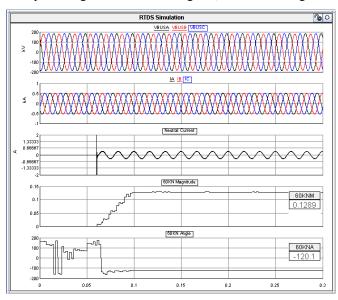

An element in B-phase right section of the SCB is shorted, causing an unbalance current magnitude of 161 mA and a phase angle close to 60 degrees, as shown in Fig. 22.

Fig. 22. Ungrounded double wye SCB with a faulty element in B-phase of right section

An element in C-phase left section of the SCB is shorted, causing an unbalance current magnitude 130 mA and a phase angle close to 120 degrees, as shown in Fig. 23.

Fig. 23. Ungrounded double wye SCB with a faulty element in C-phase of left section

An element in C-phase right section of the SCB is shorted, causing an unbalance current magnitude 163 mA and a phase angle close to -60 degrees, as shown in Fig. 24.

Fig. 24. Ungrounded double wye SCB with a faulty element in C-phase of right section

We can use the same concept for many other types of capacitor bank configurations like H-bridge, Double-WYE ungrounded with neutral voltage, etc.

#### VIII. CONCLUSION

A large number of SCB configurations are possible, and these configurations can be grounded or ungrounded, fused or without fuses, and with either voltage or current unbalance protection.

Although the way in which fused and fuseless elements/units fail is different, the principle of protection remains the same: prevent an overvoltage of greater than 110 percent on the healthy elements or units.

Millman's theorem provides an easy way to calculate the unbalance current and voltage during commissioning.

The new faulted-phase indication algorithm correctly identifies the phase (and section) with the faulted element/unit, thereby significantly reducing the outage time necessary for replacing a faulty unit.

### IX. REFERENCES

- [1] IEEE Guide for the Protection of Shunt Capacitor Banks, IEEE Standard C37 99-1990.

- [2] M. Dhillon, D. Tziouvaras, "Protection of Fuseless Capacitor Banks Using Digital Relays," presented at 26th Annual Western Protective Relay Conference, Spokane, WA, October 1999.

- [3] IEEE std 18-1992, IEEE std 18-2002

- [4] E. O. Schweitzer III, J. Schafman, "Unified Shunt Capacitor Bank Control and Protection," 45th Annual Georgia Tech Protective Relaying Conference Atlanta Georgia, May 1–3, 1991.

- [5] B. Kasztenny, J. Schaefer, E. Clark, "Fundamentals of Adaptive Protection of Large Capacitor Banks," presented at the 60<sup>th</sup> Annual Georgia Tech Protective Relaying Conference Atlanta, May 3–5, 2006.

- [6] A.H Morton, Advanced Electrical Engineering, London: Sir Isaac Pitman & Sons Ltd., 1966, p. 13.

#### X. BIOGRAPHIES

Satish Samineni received his B.E degree in electrical and electronics engineering from Andhra University College of Engineering, Visakhapatnam, India. He received his Master's degree in Electrical Engineering from University of Idaho, USA, in 2003. Since 2003 he has been with Schweitzer Engineering Laboratories, Inc. in Pullman, USA, where he presently holds the position of Lead Power Engineer. His research interests include power electronics and drives, power system protection, synchrophasor-based control applications, and power system stability. He is a registered Professional Engineer in the State of Washington.

Casper Labuschagne earned his Diploma (1981) and Masters Diploma (1991) in Electrical Engineering from Vaal University of Technology, South Africa and is registered as a Professional Technologist with ECSA, the Engineering Counsel of South Africa. After gaining 20 years of experience with the South African utility Eskom, where he served as Senior Advisor in the protection design department, he began work at SEL in 1999 as a Product Engineer in the Substation Equipment Engineering group. He transferred in 2003 to the Research and Development group where he held the position of Senior Power Engineer. In 2009 he was promoted to Transmission Engineering Development Manager. His responsibilities include the specification, design, testing, and support of transmission protection and control devices. Casper holds four US patents and has three more patents pending. He has written and co-written several technical papers in the areas of protection and control.

**Jeff Pope** is the Senior Product Engineer for the Transmission Product Group at Schweitzer Engineering Laboratories (SEL). Jeff is a member of the IEEE Power Engineering Society, and has been involved with the commissioning, control, protection, monitoring and automation of power system apparatus for 20 years. Jeff received his BSEET in 1986 from the DeVry Institute of Technology, a Master of Engineering from University of Wisconsin-Madison in 2005.