# Channel Asymmetry Compensation for Line Current Differential Relays Without External Time Sources

Anirudhh Ravi, Veselin Skendzic, Vinod Yedidi, Colby Clark, and Balaji Janarthanan Schweitzer Engineering Laboratories, Inc.

Presented at the

78th Annual Georgia Tech Protective Relaying Conference

Atlanta, Georgia

May 7–9, 2025

Originally presented at the 78th Annual Conference for Protective Relay Engineers at Texas A&M, March 2025

# Channel Asymmetry Compensation for Line Current Differential Relays Without External Time Sources

Anirudhh Ravi, Veselin Skendzic, Vinod Yedidi, Colby Clark, and Balaji Janarthanan, Schweitzer Engineering Laboratories, Inc.

Abstract—Line current differential relays exchange line current data samples to perform differential protection. The data received from the remote end are time-aligned with the locally sampled data to accurately calculate the differential current. For data alignment, line differential relays typically use two methods: namely, external time-based synchronization and channel-based synchronization. The time-based synchronization method relies on external time sources and reported time quality within the time message. It offers the advantage of estimating the channel asymmetry using the external time signal. The channel-based synchronization method does not rely on the need for external time sources. However, it is not reliable for applications using data multiplexers for long-distance line differential protection in which the channel asymmetry resulting from communications path switching is of concern. Therefore, a novel channel asymmetry detection and compensation method has been developed for precise data alignment independent of any external time sources. This paper describes the existing data alignment methods widely used by line current differential relays, proposes a novel method for data alignment, evaluates the performance of the novel method using real-time test results obtained using an industry-standard data multiplexer, and compares the performance of the proposed method with the performance of another relay using the external time-based synchronization method for data alignment.

#### I. Introduction

Line current differential protection (87L) is the preferred choice when it comes to protecting a power line because the scheme offers excellent selectivity, speed, and sensitivity. The benefits of 87L protection are especially pronounced with inverter-based resource applications [1]. The scheme works by comparing sampled current information on either end of the line that is being protected and deciding whether to trip or restrain [2]. The data exchanged between the relays typically contain the timing information and current samples. The timing information is used to estimate the channel delay and align the remote-end samples with the local-end samples to calculate the differential and restraint currents [3]. The data are typically transferred over optical fiber. Such a communications medium ensures high-speed data transmission with minimal signal attenuation. As signal attenuation increases with length, a direct point-to-point communications link is usually used for power lines that are within the relay manufacturer's specifications for the range of the fiber-optic port. Power lines that are longer than the supported direct point-to-point range can use data multiplexers. Data multiplexers help boost the signal strength in addition to offering other advantages, such as channel redundancy and time distribution. Line differential relay manufacturers often follow IEEE C37.94, IEEE Standard for N times 64 kbps Optical Fiber Interfaces between Teleprotection

and Multiplexer Equipment [4], to encode and decode the data exchanged between the relays [5]. This standardized encoding and decoding ensures that the relay is compatible with industry-standard data multiplexers.

Data multiplexers typically provide channel redundancy by supporting primary and backup communications paths in which each path comprises a fiber-optic pair of paths for transmission and reception of data. When there is a detected loss of communications (or path failure) on the primary path due to a physical channel break, channel electronics failure, or optical amplifier failure, the data multiplexers transfer the traffic from the primary path to the backup path. Based on the criticality of the application, if there is a loss of communications, the user can choose to transfer both transmit and receive links to the backup path or choose to transfer only the link that is unavailable to the backup path. The former choice avoids continuous channel asymmetry but may introduce momentary communications interruptions while the multiplexer transfers all traffic (receive and send traffic) to a backup path and may increase the overall channel latency because the backup path is usually connected through other data multiplexers. The latter choice avoids any momentary communications interruptions and may minimize the impact of an increase in the overall channel latency but can introduce continuous channel asymmetry [6].

Due to the longer distances of transmission line protection, it is more likely that communications channels will experience asymmetry and may require the use of time-based synchronization methods [7]. Since timing errors result in inaccurate data alignment, the user may need to consider securing the differential element. Improving the accuracy of time reporting can allow the application to be more sensitive [8] [9]. The external time synchronization approach works very well in systems in which the multiplexer is capable of distributing globally synchronized time. The independent satellite clock approach is inherently less robust. If there is a loss of an external time source, differential relays can fall back to the channel-based data alignment method (widely known as the ping-pong method [10]), which does not require any absolute time reference or use a standby or backup [11]. As explained in Section II of this paper, the channel-based data alignment method is intended for communications links that are symmetrical because the method inherently cannot detect or compensate for channel asymmetries. Therefore, if the communications system uses data multiplexers and if there is a channel asymmetry event, the fallback method can move the

data exchange to the backup channel, causing temporary channel asymmetry in the process.

To avoid reliance on external time sources and prevent any interruptions to the protection scheme, this paper proposes a novel method to detect channel asymmetries and determine the required compensation for accurate data alignment. The proposed method improves the overall reliability communications for line differential applications. Both channel-based and external time-based synchronization can benefit from this method. The method gives the ability for the channel-based synchronization method to detect and compensate for channel asymmetry during path switching without the need for external time sources. Likewise, the proposed method gives the ability for the time-based synchronization method to detect and compensate for channel asymmetry during path switching in loss of external time scenarios. To demonstrate the impact of data alignment methods on an 87L scheme, this paper uses the percentage-restrained characteristic with the differential or operate currents and restraint currents calculated as presented in Section III. The alpha plane method is more tolerant to channel asymmetry because it has a separate setting to add security for data alignment errors [12]. However, the improvements presented in this paper can help add sensitivity by allowing reduction of the angle setting.

#### II. DATA ALIGNMENT METHODS FOR AN 87L APPLICATION

Depending on the availability of an external time source, line current differential applications can use either of the two industry-standard data alignment methods: namely, the external time-based synchronization method or the channel-based synchronization method. If external time sources are available, a combination of both methods can also be included in the application in which one method can serve as a backup to the other; typically, the external time-based synchronization method is used as the primary method due to its accuracy and tolerance to channel asymmetries, but the channel-based synchronization method can be used as a backup in case there is a loss of external time synchronization. To perform data alignment, 87L relays calculate the channel delay and the clock offset between the relays to represent the data received from the remote relay in local time. This section describes how the 87L relays perform data alignment and determine the clock offset for either method.

#### A. Data Exchange for 87L Protection

Typically, 87L relays exchange data through fiber-optic cables by encoding and decoding the data per the IEEE C37.94 standard for broader compatibility with data multiplexers [4]. The IEEE C37.94 traffic consists of a header, overhead, and payload. The header is used to identify the start of the data based on a pattern of bits. The header alternates between each data frame, and the loss-of-signal flag is included in alternate

frames. The overhead consists of bits that indicate the number of channels used, which is helpful for data multiplexers to determine the order of multiplexing or demultiplexing. The channel data comprise the primary information, which includes the sequence number, time stamps, and sampled currents, for the 87L relays to perform data alignment and determine the differential currents. The time taken to completely receive an 87L payload depends on the number of channels and the size of the 87L payload being exchanged because each data frame can hold a maximum of 12 x 8 bits of 87L data and each frame is transmitted every 125 μs. In each relay processing interval, the relays sample the current data along with time stamps and package the data for transmission. Since the IEEE C37.94 transmit rate is 8 kHz, the data frames are continuously exchanged between the relays every 125 μs.

#### B. Channel-Based Synchronization Method

This method removes the reliance on external time sources (explained in the next subsection) by using the timing information provided by the internal crystal oscillator of the relays. Modern relays have stable temperature-compensated oscillators that have time drift or deviation less than 10 ppm with a time resolution of about 20 ns or better. The pulse from the internal crystal oscillator is usually read by the onboard field-programmable gate array and, using a phase-locked loop, the actual time is synthesized. Since the oscillator is free-running and independent across relays, the local relay that is receiving the data from the remote end needs to determine the deviation (referred to as the clock offset) of the remote time from the local time [6]. This can be compared to the concept of global time zones in which the user converts the time at a specific time zone to their local time zone. Depending on whether the local time leads or lags the remote time, the clock offset can be positive or negative, respectively.

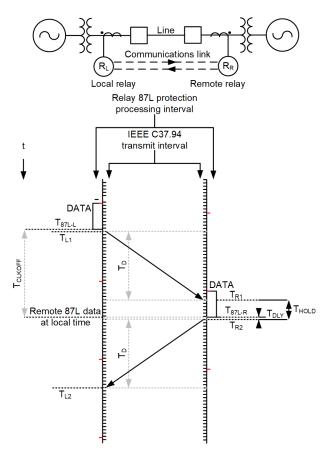

As illustrated in Fig. 1, the round-trip channel delay (T<sub>D-RT</sub>) can be estimated based on the initial transmit time stamp (T<sub>L1</sub>) and the receive time stamp  $(T_{1,2})$  since both time stamps are in the same local time zone. However, the remote relay, depending on the processing interval, responds by holding the data and then transmitting the data after a small holding delay (T<sub>HOLD</sub>), which is also included in the response packet sent by the remote relay. While estimating the round-trip channel delay, the local relay uses the holding delay information and then uses the transmit and receive time stamps to determine the round-trip channel delay, as shown in (1), and the channel delay, as shown in (2). Additionally, since the local relay can only use the time-stamp information with reference to the local time zone, any remote-end time stamps cannot be used to estimate the channel delay, unlike with the external time-based synchronization method. Therefore, the local relay must assume that the channel delay is the same on the transmit and receive paths. Hence, this method cannot guarantee accurate data alignment when channel asymmetry conditions occur.

Fig. 1. Timing diagram for channel-based synchronization, or ping-pong, method.

$$T_{D-RT} = T_{L2} - T_{L1} - T_{HOLD}$$

(1)

$$T_{D} = \frac{T_{D-RT}}{2} = \frac{T_{L2} - T_{L1} - T_{HOLD}}{2}$$

Using the estimated channel delay  $(T_D)$ , the local relay can estimate the clock offset  $(T_{CLKOFF})$  as the difference between the local receive time stamp  $(T_{L2})$  and the remote transmit time stamp  $(T_{R2})$ , as shown in (3). This delay time varies based on the relay processing interval and the IEEE C37.94 transmission interval (8 kHz).

$$T_{\text{CLKOFF}} = T_{L2} - T_{D} - T_{R2} \tag{3}$$

Since the remote data arrive at the local relay in response to the initial transmission after a specific channel delay, the remote data are always historical compared to the locally sampled data. Therefore, the corresponding local data are always available for a given set of remote data samples. The local relay can use the estimated clock offset to align the local data samples with the remote data samples to calculate the signals used to calculate differential and restraint currents.

#### C. External Time-Based Synchronization Method

In this method, the internal time source of the 87L relays can be phase-locked to the time provided by the external time source. 87L relays typically have an IRIG-B input to receive an absolute time from any external time source, such as a satellite clock or multiplexer, through a synchronous optical network (SONET). Modern 87L relays also support Precision Time Protocol per IEEE 1588, *IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and*

Control Systems [13], to receive external timing. Since the time stamp of data exchanged between the 87L relays is based on an absolute time source rather than the free-running internal crystal oscillator, there is no need to calculate the clock offset between the relays. This is the simplest method for the relay since there is no clock offset, and the relays can directly use the received data along with the time stamp to perform data alignment. The local relay can simply store the locally sampled data in a data buffer and, once the remote data are available, align the remote data with the local data for a given time stamp, and then estimate the differential and restraint currents to determine the trip decision. Since the time stamps of transmit and receive are known, the relays can precisely determine the one-way channel delay and any difference between the channel delays can be classified as channel asymmetry. Therefore, this method is most suitable for long-distance 87L applications that use data multiplexers. However, a shortcoming of this method is the reliance on the availability and quality of the time source.

### III. EFFECT OF TIME QUALITY AND CHANNEL ASYMMETRY ON DATA ALIGNMENT AND 87L PROTECTION

Data alignment is a critical step in the overall line differential protection scheme. Any inaccuracies in the data alignment can jeopardize the scheme, which can result in security concerns. For any given protection system, the typical performance parameters are dependability, security, sensitivity, selectivity, and speed. Line differential protection schemes are known for their superior selectivity, and data alignment has no direct impact on selectivity. However, data alignment can have an adverse effect on the security, sensitivity, and dependability of the scheme, as explained in this section.

#### A. Effect on 87L Security

The effect of data alignment errors on the security of the 87L scheme is further studied in this section. The external time synchronization and channel-based synchronization methods can yield accurate data alignment in ideal conditions. But the quality of time and presence of channel asymmetry can pose challenges to external time synchronization and channel-based synchronization, respectively. Such challenges can be clearly illustrated using a percentage-restrained 87L characteristic by assuming the operate and restraint currents, as shown in (4) and (5), respectively.

$$I_{OP} = |\overrightarrow{I_{LOCAL}} + \overrightarrow{I_{REMOTE}}|$$

(4)

$$I_{RT} = |\overrightarrow{I_{LOCAL}}| + |\overrightarrow{I_{REMOTE}}|$$

(5)

where:

$\overrightarrow{I_{LOCAL}}$  is the local current phasor.

I<sub>REMOTE</sub> is the remote current phasor.

Data alignment errors lead to imperfect alignment of local and remote samples and phasors, creating false angle errors affecting the estimation of the differential or operate and restraint currents. Large data alignment errors can lead to fictitious operate and restraint currents that may lead to potential misoperation. It is important to note that this can be tackled by adjusting the slope of the 87L characteristic, but such

a decision can jeopardize the sensitivity and dependability of the 87L scheme.

1) Time Ouality Provided by an External Time Source Modern clocks that supply a time reference through IRIG-B can ensure an average time accuracy of 40 ns or better. However, there can be various vulnerabilities [14] to the time synchronization, such as shadowing, unintended or malicious interference, or solar flux. Under such circumstances, the clock goes into a holdover state in which the onboard oscillator of the clock can free-run, thereby continuing to provide a valid time stamp to the relays. However, compared to a satellite clock (for example, GPS), the stability of the internal oscillator is lower. Therefore, the time of the clock starts drifting with respect to the UTC time. This drift can range, depending on the type of clock source, from as slow as 200 ns over 24 hours if stable atomic oscillators like rubidium or cesium are used [15]. Typically, temperature-compensated oscillators (TCXOs), which cost the least but have the poorest holdover accuracy; oven-compensated oscillators (OCXOs), which are moderately priced but have better holdover accuracy; or double oven-compensated oscillators (DOCXOs), which are the most expensive but have the best holdover accuracy, are used in the satellite clocks used for time synchronization in 87L applications in which the holdover accuracy after 24 hours can range between less than 5 µs and more than 300 µs [16].

To understand the effect of the time drift on the 87L characteristic, the local current phasor can be assumed to be the reference with a phase angle of zero while an error term can be introduced in the angle of the remote current phasor where the error term quantifies the alignment error introduced by the time drift. This angle error can be obtained using (6).

$$\theta_{\text{error}} = T_{\text{drift}} \times F_{\text{N}} \times 360^{\circ} \tag{6}$$

where:

T<sub>drift</sub> is the drift time in seconds.

$F_N$  is the relay nominal frequency (for relays with a variable sampling rate,  $F_N$  can be the data tracking frequency).

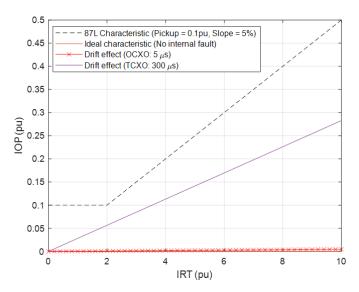

Fig. 2 illustrates how an ideal characteristic (local phasor as reference and remote phasor  $180^{\circ}$  out of phase) is shifted by the drift introduced by the onboard oscillator of the clock when the source providing the absolute time reference is lost for 24 hours. It can be seen that due to the superior stability of OCXOs over TCXOs, the angle error ( $\theta_{error}$ ) is expected to be minimal. Even if the characteristic is set to be sensitive, the holdover accuracy offered by crystal oscillators does not seem to cause any significant angle errors. It is important to note that this conclusion is drawn for drift over 24 hours, and it was assumed that any vulnerability that caused the loss of a time source would be fixed within 24 hours following the occurrence. If not, then the drift can be multiples of 24 hours higher than the values indicated in Fig. 2.

Fig. 2. Effect of time drift in clock holdover state after 24 hours.

#### 2) Presence of Channel Asymmetry

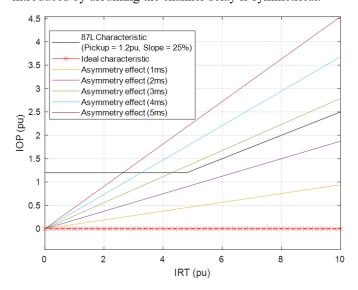

To illustrate the effect of channel asymmetry on an 87L characteristic, it is important to understand how channel asymmetry introduces error in the data alignment when channel-based synchronization is used. Since the data alignment is performed based on the estimated clock offset, any error in data alignment means there is an error in the estimated clock offset. Fig. 3 illustrates a symmetrical communications link case since the channel delay (T<sub>D</sub>) was assumed to be the same in both paths (local to remote and remote to local). Under asymmetrical channel conditions, the channel delay is different for the two paths. Since the ping-pong method cannot determine the channel delay in individual paths, there is an inherent error introduced by assuming the channel delay is symmetrical.

Fig. 3. Effect of channel asymmetry on differential element response.

For example, considering the local relay as the reference, assume the channel delay on the transmit path (local to remote) is 2 ms while the channel delay on the receiving path (remote to local) is 1 ms. The relay using the ping-pong method calculates the round-trip channel delay as 3 ms and assumes the channel is symmetrical; therefore, it calculates the channel delay as 1.5 ms. Since the local relay receives data after a channel delay of 1 ms, assuming the channel delay is 1.5 ms results in aligning the remote data beyond the actual time. Therefore, the local relay overestimates the channel delay. On the other hand, the remote relay receives data after a channel delay of 2 ms; therefore, assuming the channel delay as 1.5 ms results in aligning the remote data (received from the local relay) ahead of the actual time. Therefore, the remote relay underestimates the channel delay. With an example, it is intuitive to understand how (3) can be modified to introduce the error term (Terror), which is a resultant of assuming an asymmetrical channel is symmetric, as shown in (7) and (8). For the example case, the error  $(T_{error})$  is 0.5 ms where an overestimation (estimated delay > expected delay) of channel delay results in a positive error and a lower-than-expected clock offset, while an underestimation (estimated delay < expected delay) of the channel delay results in a negative error and a higher-than-expected clock offset. Similar to the previous section, the error term (T<sub>error</sub>) can be converted into an angle error and the error for various channel asymmetries can be plotted on an 87L characteristic, as shown in Fig. 3.

$$T_{\text{CLKOFF}} = T_{\text{CLKOFF\_IDEAL}} - T_{\text{error}}$$

(7)

$$T_{\text{error}} = \text{Estimated Delay} - \text{Expected Delay}$$

(8)

$$T_{error}$$

= Estimated Delay - Expected Delay (8)

#### B. Effect of Channel Asymmetry on 87L Sensitivity

If there is no backup communications channel or if the relay does not support any reliable channel asymmetry compensation method, the user may need to account for the fictitious operate current introduced due to the data misalignment caused by channel asymmetry in the slope setting to secure the 87L characteristic. This can be done as explained in this section.

Under ideal through-load conditions and with no channel asymmetry, the local and remote currents are equal in magnitude and 180° out of phase. The operate current can be expressed as shown in (9).

$$IOP = |\overrightarrow{I_{LOCAL}} + \overrightarrow{I_{REMOTE}}|$$

$$= |I_{MEAS} \cdot e^{j0^{\circ}} + I_{MEAS} \cdot e^{j180^{\circ}}|$$

(9)

where I<sub>MEAS</sub> is the measured magnitude of the through-load current.

If there is channel asymmetry, (9) can be expressed as shown in (10).

$$IOP = |I_{MEAS}|e^{j\theta'_{error}} + |I_{MEAS}|e^{j(180^{\circ} - \theta'_{error})}$$

(10)

where  $\theta'_{error}$  is the resultant angle error introduced by channel asymmetry.

It is important to note that  $\theta'_{error}$  is different from  $\theta_{error}$ presented in (6) in which  $\theta'_{error}$  is the angle error introduced in data alignment as a result of channel asymmetry.

Equation (10) can be expressed in Euler's formula as shown in (11).

$$IOP = |I_{MEAS}|[e^{j\theta'_{error}} - e^{j-\theta'_{error}}]$$

$$= |I_{MEAS}|[2j\sin(\theta'_{error})]$$

(11)

As mentioned in the previous section, since the local current data are the references, the remote current phasors are misaligned by an erroneous angle; however, to present (8) in Euler's formula, an angle error is assumed on both local and remote phasors. Also, as mentioned previously, the angle error is a result of half of the total channel asymmetry. Therefore, (10) can be modified to relate slope and the amount of channel asymmetry, as shown in (12).

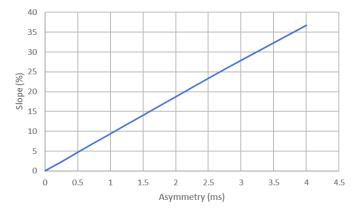

$$\begin{split} & Slope = sin \left( \frac{\theta'_{error}}{4} \right) = sin \left( \frac{Asymm \times F_N \times 360^\circ}{4} \right) \\ & where \ Asymm \ is \ the \ total \ amount \ of \ channel \ asymmetry \ in \end{split}$$

seconds.

Using (12), the required slope setting to secure the 87L characteristic for various channel asymmetry magnitudes can be determined and plotted, as shown in Fig. 4. To maintain security of the 87L element, as the magnitude of channel asymmetry increases, the 87L characteristic needs to be linearly desensitized.

Fig. 4. Slope setting versus channel asymmetry.

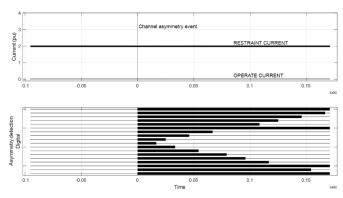

#### C. Effect of Channel Asymmetry on 87L Dependability

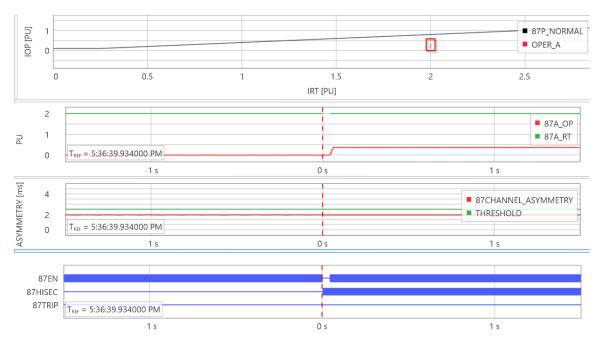

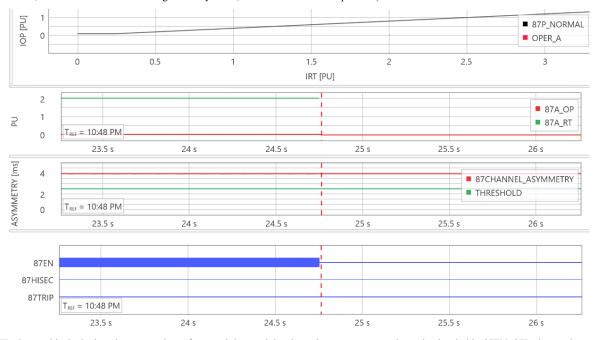

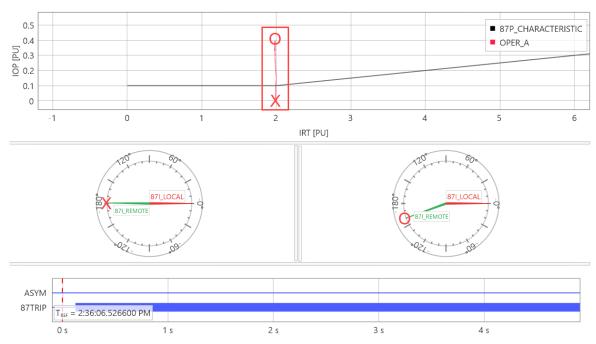

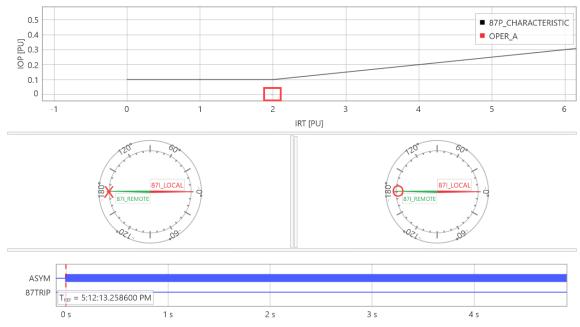

The 87L element design for schemes with external time-based synchronization methods needs to consider the scenario when the channel asymmetry is present and an external time source is lost. In case of the loss of an external time source, the relay may fall back to the ping-pong method for data alignment. The magnitude of the channel asymmetry prior to a fallback condition can impact the security and dependability of the 87L protection scheme. Upon entering the fallback (ping-pong) method, the relay may force the 87L element into high-security mode (see Fig. 5) if the estimated channel asymmetry is within a certain threshold or block the 87L element if the estimated channel asymmetry is above the threshold (see Fig. 6).

The 87L schemes with external time-based synchronization can benefit from using the proposed method in this paper by accounting for the channel asymmetry even in fallback scenarios, further enhancing both the security and dependability of the scheme.

Fig. 5. 87L element switched to high-security mode when there was a loss of external time and the channel asymmetry was below the threshold. (87EN: 87L element is enabled; 87HISEC: 87L element in high-security mode; 87TRIP: differential trip issued)

Fig. 6. 87L element blocked when there was a loss of external time and the channel asymmetry was above the threshold. (87EN: 87L element is enabled; 87HISEC: 87L element in high-security mode; 87TRIP: differential trip issued)

## IV. PROPOSED KALMAN FILTER-BASED CHANNEL ASYMMETRY DETECTION AND COMPENSATION LOGIC

Channel-based synchronization schemes can make use of the proposed Kalman filter-based channel asymmetry detection and compensation logic all the time. An external time-based synchronization scheme can make use of the proposed method if there is a loss of external time and the scheme falls back to the channel-based mode. Since the external time-based data alignment scheme can handle channel asymmetries, if the ping-pong method can be enhanced to handle channel asymmetries, then any dependability or security concerns due to channel asymmetries can be completely removed. As the ping-pong method relies on the timing provided by the relay's onboard oscillator and modern relays have stable oscillators, the proposed method enhances the existing ping-pong method by detecting any sudden jumps in the clock offset and compensating the error introduced by assuming a symmetrical channel.

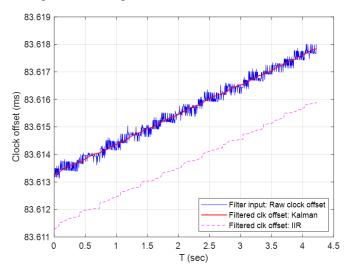

This jump can be quantified by  $T_{error}$  (refer to (8)). Under symmetrical channel conditions, the estimated clock offset is  $T_{error} = 0$ . Given that the oscillator is stable, the clock offset continues to drift at an expected rate specified by the drift rate of the oscillator. However, under asymmetrical channel

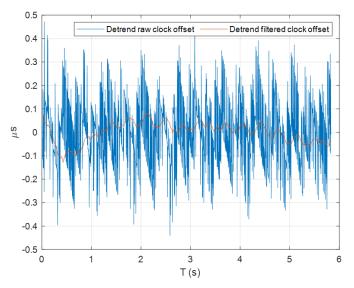

conditions, the estimated clock offset is  $T_{error} \neq 0$ , resulting in an instantaneous deviation from the expected drift rate. As the proposed Kalman filter-based channel asymmetry detection and compensation logic method looks for sudden jumps in the clock offset, it is designed to detect channel asymmetries resulting from path-switching events and does not detect standing or steady-state channel asymmetries that arise due to fiber length differences. Typically, due to clock jitter, the raw clock offset can have variations as illustrated in Fig. 7, and therefore, the calculated clock offset is passed through a smoothening filter to obtain a filtered clock offset for data alignment. A smoothening filter, such as an infinite impulse response (IIR) filter, works, but as illustrated in Fig. 7, since the IIR filter is an averaging filter, the filter output lags the input raw clock offset (estimated by the ping-pong method) while the proposed adaptive Kalman filter closely tracks the input, thanks to the predictive component of the Kalman filter.

Fig. 7. Clock offset trend over time.

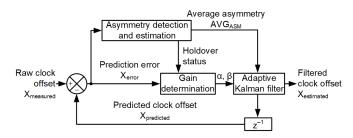

Kalman filters are commonly used to estimate and predict the system states when the system state cannot be directly measured or the measurement is not reliable [17] [18]. Typical system states are position, velocity, and acceleration. Here, the position of the system is the clock offset. The rate-of-change of clock offset is the velocity term, which is estimated to predict the future state of the system. Since two system states need to be estimated, two gains and two measurements are necessary. Since the velocity of the clock offset cannot be directly measured, it needs to be computed based on the raw clock offset, and therefore, the raw clock offset serves as the primary input quantity for the filter. The two gains, namely, alpha and beta, are used to give weightage to the correction performed by the filter based on the error difference between the predicted system states and the observed system states. Alpha is associated with the error in system position, and beta is associated with the error in system velocity. Since the position error can be invalid (due to an invalid input of raw clock offset introduced during path-switching events), the alpha should be adaptive and should not give any weight to the error component but rely only on the prediction. Therefore, the traditional Kalman filter can be made adaptive, as shown in Fig. 8.

Fig. 8. Block diagram of the proposed adaptive clock offset estimation method.

The adaptive Kalman filter can be implemented based on Equations (13)–(17) [19].

$$X_{\text{estimated}}(k) = X_{\text{predicted}}(k-1)$$

$$+\alpha(X_{\text{error}}(k) - AVG_{\text{ASM}})$$

(13)

where:

$X_{\text{estimated}}(k)$  is the filtered clock offset for processing Interval k.

$X_{error}(k) = X_{measured}(k) - X_{predicted}(k-1)$  is the error in the predicted clock offset for processing Interval k.

$X_{predicted}(k)$  is the predicted clock offset for processing Interval k.

$\alpha$  is the gain for position prediction error.

AVG<sub>ASM</sub> is the average estimated channel asymmetry.

The primary design constant of a Kalman filter is the  $\alpha$  gain parameter, as  $\beta$  can be determined based on  $\alpha$ , as shown in (15). An initial gain constant value can be assumed and further tweaked, based on the objective, which is to make the filter the least sensitive possible to any sudden changes in the clock offset. Based on the initial sum of squared errors, a generalized gradient method [20] can be used to determine the optimal value of  $\alpha$  that would yield the minimum sum of squared error.

$$V_{\text{estimated}}(k) = V_{\text{predicted}}(k-1)$$

$$+\beta \left( \frac{X_{\text{error}}(k) - AVG_{\text{ASM}}}{T} \right)$$

$$\beta = 2(2-\alpha) - 4\sqrt{(1-\alpha)}$$

(15)

where:

V<sub>estimated</sub>(k) is the estimated rate-of-change of the clock offset.

$\beta$  is the gain for velocity prediction error.

T is the processing interval of the relay.

$$X_{\text{predicted}}(k) = X_{\text{estimated}}(k) + (V_{\text{estimated}}(k) \times T)$$

(16)

$V_{\text{predicted}}(k) = V_{\text{estimated}}(k)$  (17)

where:

$X_{predicted}(k)$  is the predicted clock offset.

$V_{\text{predicted}}(k)$  is the predicted rate-of-change of the clock offset.

Based on the design objectives and the determined gains, it can be seen that the proposed filter can significantly minimize the noise in the raw clock offset, as shown in Fig. 9. As illustrated, the proposed filter minimizes the peak-to-peak noise from 1  $\mu$ s to within 0.2  $\mu$ s.

Fig. 9. Performance of the proposed filter with respect to noise reduction.

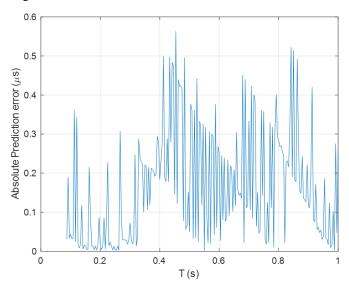

The prediction error  $(x_{predicted}(k))$  is the fundamental quantity used to detect channel asymmetry since it has been observed through a simulation that the filter predicts exceptionally well, thereby having a very low prediction error (less than 1 µs), as illustrated in Fig. 10. When there is channel asymmetry and the clock offset instantaneously jumps, the Kalman filter uses the predicted clock offset to calculate the prediction error and this prediction error is the magnitude of the channel asymmetry. The sign of the prediction error indicates the direction of the asymmetry. As the Kalman filter accurately predicts the clock offset, the filter can be operated in a holdover state in which the alpha and beta gains can be set to zero, which results in the system operating purely based on prediction. During this holdover state, an average of the prediction errors can be obtained to estimate the average channel asymmetry magnitude, AVG<sub>ASM</sub>.

Fig. 10. Clock offset prediction error achieved by the adaptive Kalman filter.

#### V. RESULTS AND DISCUSSION

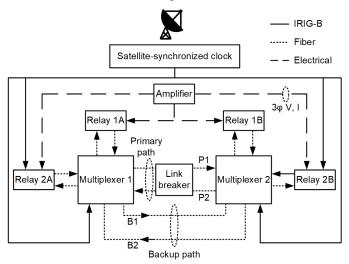

To illustrate the proposed method, as shown in Fig. 11, a test setup comprising two relays (one 87L pair) that support the proposed method and two relays (one 87L pair) that support channel asymmetry compensation using external time source was developed. These relays were set up to communicate through a time-domain data multiplexer using single-mode fiber cables. An amplifier was used to inject current signals to all the relays. However, before testing the proposed algorithm, the basis of the algorithm was verified to ensure that the crystal oscillator onboard the relay was very stable and any sudden disturbances could be declared a path-switching event. The stability of the crystal oscillator at varying temperatures was tested. This involved placing the relays that support the proposed method in a thermal chamber and varying the temperature between -45° and +85°C. During this time, the channel delay and the estimated clock offset in the relays were continuously monitored to study their stability over varying temperatures. This section begins by illustrating the test results obtained from the thermal ramp test.

Fig. 11. Hardware test setup.

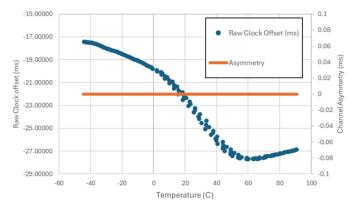

#### A. Thermal Ramp to Verify Oscillator Stability

The proposed method described earlier is highly dependent on the stability of a differential relay's internal clock oscillator. To determine the stability of the crystal oscillator, a test was performed in which differential relays were placed in a thermal chamber and the raw clock offset (the input to the Kalman filter) was recorded as the temperature was ramped between -45° and +85°C. The relays were set up to communicate over a direct point-to-point optical fiber link with no intentional channel asymmetry. Throughout the test, the temperature of the chamber ramped at a rate of 1°C/min. Thermocouples were placed in the top and bottom of the chamber as well as inside the relays to monitor the applied temperature. The estimated channel asymmetry (AVG<sub>ASM</sub>) was also captured to determine if the proposed method falsely detected any channel asymmetries, as there were no channel asymmetries created during the thermal test. The captured raw clock offset and the estimated asymmetry were plotted, as shown in Fig. 12. It can be seen that for the given temperature range and drift in clock

offset, channel asymmetry for the tested relays remained at zero since there were no sudden jumps in the clock offset as the temperate was ramped. This clearly illustrates the efficiency with respect to temperature compensation of modern oscillators.

Fig. 12. Clock offset and channel asymmetry over temperature.

#### B. Detecting and Compensating Channel Asymmetries

As illustrated in Fig. 11, the relays were set up to communicate through a multiplexer that has the capability of path switching, i.e., moving traffic to a backup path if the primary path is unavailable. The primary path, labeled as P1 and P2, is configured to be the primary reference time clock receiving GPS time transporting OC-48 SONET traffic. The backup path, labeled as B1 and B2, is configured to be a virtual synchronous network. This feature allows the traffic to be encapsulated in a time-division multiplexing container for transport over Ethernet with a deterministic delay (known as a packet delay variation, PDV). Such a configuration allows testing various asymmetric delays by setting the backup path to transport 87L packets with various channel delays without having to physically change the fiber length. The multiplexer used to test the proposed method supports user-programmable modes that characterize the response of the multiplexer for a loss of signal (physical channel break).

The proposed method was tested in both modes of operation. When there is a physical channel break, the receiving multiplexer has a loss of signal, which is communicated to the transmitting multiplexer. The receiving multiplexer initiates a loss-of-signal alarm while the transmitting multiplexer initiates a far-end failure alarm. Once the far-end failure is detected, the transmitting multiplexer, based on the user setting for a response following a loss of signal, transfers the traffic from the broken primary path to the backup path with the highest priority or informs the other multiplexer so that traffic on both the broken and healthy primary paths is simultaneously transferred to the backup path with the highest priority. As explained previously, the former switching results in steady-state channel asymmetry while the latter switching may result in momentary channel asymmetry. The accuracy of the proposed method was studied in each of these scenarios.

In Scenario A, the multiplexer is set to switch only the broken path; for example, P1. Upon switching to B1, there is steady-state channel asymmetry due to a constant channel delay difference between the transmit (B1) and receive (P2) paths.

In Scenario B, the multiplexer is set to switch both transmit (P1) and receive (P2) paths to B1 and B2, respectively, for a loss of signal, resulting in momentary circuit interruption and momentary channel asymmetry. This helps evaluate the speed of asymmetry detection of the proposed method, as the path switching typically happens within a second.

The multiplexer is preferably configured as in Scenario B in real-world applications because it avoids the presence of any prolonged channel asymmetry.

#### 1) Scenario A: Steady Asymmetry

As shown in Fig. 11, a link breaker device that can break the transmit or receive paths individually is placed in the primary path. This device communicates serially to a PC that sends commands to the device to break the required paths for testing. When the link breaker device breaks one of the communications links, the multiplexer will detect a far-end failure and then switch the traffic to a backup path. In this paper, the link status of the primary path P1 is controlled to illustrate the performance of the proposed method. To start with, the proposed asymmetry detection method was disabled in Relays 1A and 1B and the phasor information, i.e., the operate and restraint currents, was captured for an asymmetry event with 1 pu through current applied. The channel asymmetry was created by breaking the primary path P1, resulting in the multiplexer moving the traffic from P1 to B1 and B1 has a 2 ms channel delay, resulting in channel asymmetry of 2 ms.

Fig. 13 illustrates the phasor information as computed by Relay 1A during the asymmetry event. Since P2 is available, Relay 1A receives data from Relay 1B through P2, which has an approximately 0 ms delay. Since the ping-pong method cannot determine a unidirectional channel delay, it assumes that the total round-trip delay of 2 ms is equal in B1 and P2. Therefore, Relay 1A assumes that the data arrive after a channel delay of 1 ms instead of 0 ms. By doing so, the relay overestimates the channel delay, resulting in the remote phasor moving counterclockwise by 20°. From Fig. 13, it can be seen that if the 87L characteristic is set to be as sensitive as possible (i.e., with a pickup of 0.1 pu and slope of 5 percent), there is a possibility that the relay may misoperate for such an event, as indicated by the movement of the operating quantity on the characteristic (vertical line within the box) and the activation of the 87TRIP (87 operate) digital.

The alignment error shown in the previous event can be avoided if the proposed method is used. Fig. 14 illustrates that with the proposed method, before and during channel asymmetry, the phasors are aligned 180° out of phase with each other and the operate current is approximately 0 pu, as expected. The proposed method can thus improve the overall reliability of the 87L scheme.

Fig. 13. Relay 1A event analysis comparing differential phasors pre-asymmetry (O) and during asymmetry (X) without proposed compensation.

Fig. 14. Relay event analysis comparing differential phasors pre-asymmetry (O) and during asymmetry (X) with the proposed method.

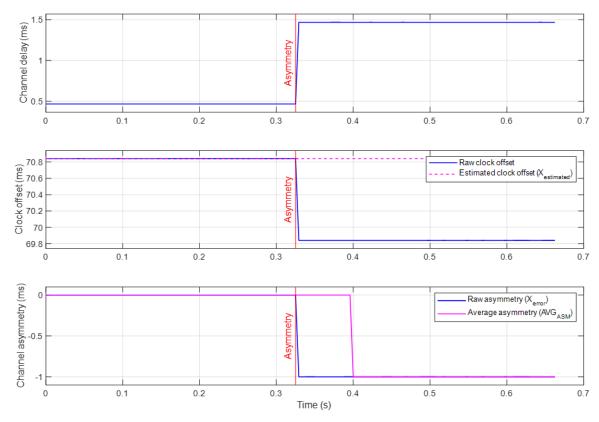

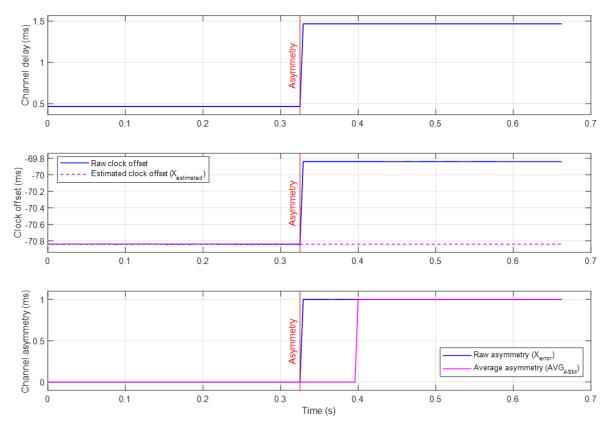

The behavior of the proposed method is illustrated in Fig. 15, in which it can be seen that when there is a change in channel asymmetry, there is a sudden jump in the channel delay due to error introduced by the ping-pong method, as explained in the previous section. As the channel delay jumps, the raw clock offset calculated using (3) also jumps. Based on (3), it can be seen that the jump in the clock offset is in the opposite direction for Relays 1A and 1B. The sudden change in the raw clock offset is detected by the proposed method as the prediction error (X<sub>error</sub>) suddenly changes. Upon detecting the change, the proposed method places the filter in a holdover state in which, based on the known velocity, the clock offset estimated by the proposed method (X<sub>estimated</sub>) maintains the

trajectory of the clock offset, as shown by the estimated clock offset plot (Fig. 10). During the holdover state, the proposed method averages the prediction error (X<sub>error</sub>) and estimates an average channel asymmetry (AVG<sub>ASM</sub>), which is used to estimate the clock offset (X<sub>estimated</sub>). As explained before, since Relay 1A overestimates the channel delay, the clock offset estimated using the ping-pong method decreases. This results in the prediction error (X<sub>error</sub>) and the average asymmetry (AVG<sub>ASM</sub>) having the same signs, and this results in the clock offset (X<sub>estimated</sub>) following the expected trajectory, as shown in (13). Similarly, as Relay 1B underestimates the channel delay, the clock offset increases.

Fig. 15a

Fig. 15b

Fig. 15. Relay event analyses comparing differential phasors pre-asymmetry and during asymmetry with the proposed method for (a) Relay 1A and (b) Relay 1B.

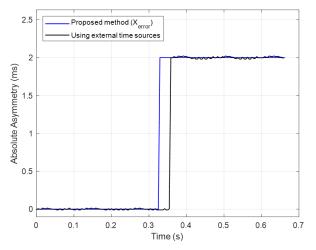

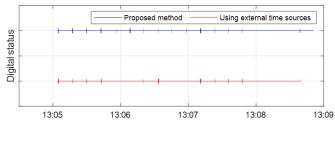

Fig. 16 illustrates that the proposed method detects and continuously tracks the channel asymmetry since the prediction error ( $X_{error}$ ) changes instantaneously whenever there is a jump in the clock offset ( $X_{measured}$ ) caused by path switching. The detected prediction error is then averaged (AVG<sub>ASM</sub>) and used by the data alignment scheme to estimate the clock offset ( $X_{estimated}$ ). Fig. 17 compares the performance of the proposed method, as implemented in Relays 1A and 1B, with the existing time-based synchronization method, as implemented in Relays 2A and 2B. The plot that has been provided for illustration is a digital plot with a thicker line indicating an assertion (true state or Boolean 1) and a flat line indicating a deassertion (false state or Boolean 0).

Fig. 16. Estimation comparison between Relays 1A and 2A for a 2 ms simulated channel asymmetry event.

Fig. 17. Detection comparison between Relays 1A and 2A for a 2 ms simulated channel asymmetry event.

Various channel asymmetries that are possible in a real-world system were simulated using the test setup, and the performance of the proposed method was compared with that of using external time sources to determine the channel asymmetry. Typically, channel asymmetries are within 2 ms, although in rare instances, there can be a worst-case asymmetry

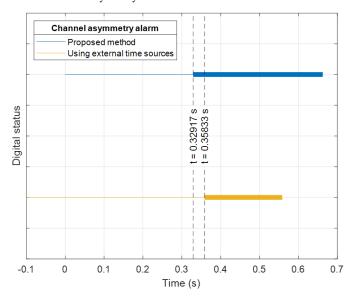

of up to 5 ms [10]. As illustrated in Fig. 18, channel asymmetries ranging between 0.5 ms and 4 ms were simulated with 0.5 ms increments. It can be seen that the proposed method can accurately detect channel asymmetries as the channel asymmetry reported by the proposed method closely matches the simulated channel asymmetry with an absolute error of less than  $0.5~\mu s$ .

Fig. 18. Evaluating the performance of the proposed method for various simulated channel asymmetry events.

#### 2) Scenario B: Momentary Asymmetry

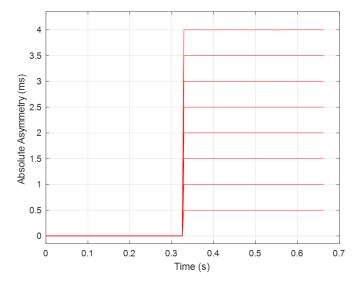

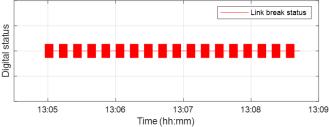

In this case, the multiplexer switches both the broken primary path and the healthy primary path to backup paths. The link status of the primary path P1 was controlled using the same link breaker device used in the previous subsection. The multiplexer transfers the traffic on P1 and P2 to B1 and B2, respectively, to avoid any steady channel asymmetry. However, when the multiplexer transfers the traffic, there can be momentary channel asymmetry as the multiplexer can first move traffic from P1 to B1 and then move traffic from P2 to B2. Since the channel asymmetry can be momentary (typically within a second), it is imperative that the proposed method quickly detect the channel asymmetry and compensate for the channel asymmetry error so that the differential protection is secured.

Twenty path-switching events were created to test the speed of path-switching detection by the proposed method. The events were created by controlling the link breaker device using a computer program. The multiplexer was treated as a black box during the testing. It was unknown which of the 20 path-switching events would result in channel asymmetry, nor was the duration of the channel asymmetry known. To test that the data alignment was accurate, the status of the 87L element was closely monitored during the test where 1 pu through-load current was applied at 60 Hz and any missed or erroneous channel asymmetry detection and estimation could result in a false operate current, leading to a misoperation. To precisely catch any errors, the 87L element was set to be very sensitive with the one-way backup path delay set to 4 ms (with the percentage-restrained characteristic set to a 0.1 pickup and

5 percent slope; this creates up to a 90° misalignment error, resulting in a misoperation if the channel asymmetry is not accurately compensated). To compare the performance of the proposed method with that of the existing time-based synchronization method, the channel asymmetry alarms provided by both methods were monitored. Since the alarm status provided by the manufacturer offering the time-based synchronization method has a fixed pickup and dropout delay, the alarm status is not reported for path-switching events that result in channel asymmetry lasting less time than the pickup delay. Therefore, it must be understood that the comparison with the external time-based synchronization method was provided for illustrative purposes, and it is expected that events resulting in an alarm from the external time-based synchronization method will always result in an alarm from the proposed method. Fig. 19 illustrates that the 87L differential quantities, such as operate and restraint currents, are extremely stable during 20 path-switching events simulated using the link breaker device, thanks to the precise asymmetry detection by the proposed method. It can be seen that the proposed method can detect channel asymmetries as momentary as 10 ms, which cannot even be seen in the digital plot (shown in Fig. 20).

Fig. 19. Demonstration of the stability of 87L quantities with the proposed method for several path-switching events resulting in channel asymmetry at t = 0 s.

Fig. 20. Performance of the proposed method for real-time path-switching events.

#### VI. CONCLUSION

This paper discusses the popular methods, namely, time-based synchronization and channel-based synchronization (or the ping-pong method), used for data alignment by line differential protection relays and presents the advantages and disadvantages of both methods. Then, the effect of data alignment on the security and dependability of the differential element was illustrated, and it was observed that channel asymmetries pose significant challenges to the integrity of the differential element. The performance of existing time-based synchronization and channel-based synchronization methods were studied under channel asymmetries, and the inability of the channel-based synchronization method to reliably detect channel asymmetries was clearly demonstrated. The objective of the proposed method is to address the shortcomings of the channel-based synchronization method with respect to reliably detecting and compensating for channel asymmetries. The proposed method looks for sudden jumps in the clock offset and is designed to detect channel asymmetries resulting from path-switching events. It does not detect standing or steadystate channel asymmetries.

The techniques used by the proposed method to enhance the channel-based synchronization method were presented, and the performance was clearly demonstrated using a real-time line current differential protection setup. Based on the results, it was confirmed that the proposed method can reliably detect and compensate for prolonged and momentary channel asymmetries that can be caused by multiplexer path-switching events. By doing so, it was shown that the proposed method significantly improves the security of line differential relays that use the channel-based synchronization method to perform differential protection. The improvement of availability of the protection scheme was also demonstrated by comparing the performance of the proposed method with that of the time-based synchronization method when there is a loss of an external time source for the relay. Since the proposed method does not rely on external time sources, the proposed method continued to detect and compensate for channel asymmetries while the relay using the time-based synchronization method had to fall back when there was a loss of an external time source and disable the differential protection based on the magnitude of the channel asymmetry prior to the fallback. This presents an opportunity for relays using the external time-based synchronization method with fallback strategies to use the proposed method and improve the overall reliability of differential protection.

#### VII. REFERENCES

- [1] R. Chowdhury and N. Fischer, "Transmission Line Protection for Systems With Inverter-Based Resources Part I: Problems" *IEEE Transactions on Power Delivery*, Vol. 36, Issue 4, August 2021, pp. 2,416–2,425.

- [2] B. Kasztenny, G. Benmouyal, H. J. Altuve, and N. Fischer, "Tutorial on Operating Characteristics of Microprocessor-Based Multiterminal Line Current Differential Relays," proceedings of the 38th Annual Western Protective Relay Conference, Spokane, WA, October 2011.

- [3] H. Miller, J. Burger, N. Fischer, and B. Kasztenny, "Modern Line Current Differential Protection Solutions," proceedings of the 36th Annual Western Protective Relay Conference, Spokane, WA, October 2009.

- [4] IEEE Std C37.94-2017, IEEE Standard for N Times 64 kbps Optical Fiber Interfaces Between Teleprotection and Multiplexer Equipment.

- [5] R. Nathan, C. Chandakabata, and R. Barnes, "Ethernet-Based Line Differential Protection Over Passive Multiplexers," proceedings of the South East Asia Protection, Automation and Control Conference, Melbourne, Australia, March 2017.

- [6] B. Kasztenny, N. Fischer, K. Fodero, and A. Zvarych, "Communications and Data Synchronization for Line Current Differential Schemes," proceedings of the 2nd Annual Protection, Automation and Control World Conference, Dublin, Ireland, June 2011.

- [7] K. Lee, D. Finney, N. Fischer, and B. Kasztenny, "Testing Considerations for Line Current Differential Schemes," proceedings of the 38th Annual Western Protective Relay Conference, Spokane, WA, October 2011.

- [8] A. Shrestha, P. Nadkar, and J. Fultz, "Understanding the Impact of Time Inaccuracy on Synchrophasors, Traveling-Wave Fault Locating, and Line Current Differential Protection," proceedings of the Protection, Automation & Control World Americas Conference, Raleigh, NC, August 2023.

- [9] R. Chowdhury, R. McDaniel, and N. Fischer, "Line Current Differential Protection in Systems With Inverter-Based Resources—Challenges and Solutions," proceedings of the 49th Annual Western Protective Relay Conference, Spokane, WA, October 2022.

- [10] IEEE Std C37.243-2015, IEEE Guide for Application of Digital Line Current Differential Relays Using Digital Communication.

- [11] B. Kasztenny, N. Fischer, and B. Le, "Fallback Algorithms for Line Current Differential Protection Applied With Asymmetrical Channels Upon the Loss of Time Reference," proceedings of the 11th IET International Conference on Developments in Power Systems Protection, Birmingham, UK, April 2012.

- [12] J. Roberts, D. Tziouvaras, G. Benmouyal, and H. J. Altuve, "The Effect of Multiprinciple Line Protection on Dependability and Security," proceedings of the Southern African Power System Protection Conference, Johannesburg, South Africa, November 2000.

- [13] IEEE Std 1588-2019, IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems.

- [14] IEEE Std 2030.101-2018, IEEE Guide for Designing a Time Synchronization System for Power Substations.

- [15] D. Williams, R. Jodrie, K. Fodero, P. Robertson, C. Huntley, and M. Elshafi, "Maintaining Precise Time for Power System Applications in the Event of Wide Area Loss of GPS," proceedings of the Protection, Automation & Control World Conference, Raleigh, NC, August 2023.

- [16] E. W. Chen, B. Smyth, M. v. Rensburg, and M. Rajasekaran, "It's About Time—Considerations and Requirements for DSS and Line Current Differential Applications," proceedings of the 76th Annual Georgia Tech Protective Relaying Conference, Atlanta, GA, May 2023.

- [17] MathWorks, "Kalman Filter." Available: mathworks.com/discovery/ kalman-filter.

- [18] R. E. Kalman, "A New Approach to Linear Filtering and Prediction Problems," *Journal of Basic Engineering*, Vol. 82, Issue 1, March 1960, pp. 35–45.

- [19] P. R. Kalata, "The Tracking Index: A Generalized Parameter for α-β and α-β-γ Target Trackers," IEEE Transactions on Aerospace and Electronic Systems, Vol. AES-20, Issue 2, March 1984, pp. 174–182.

- [20] L. S. Lasdon, R. L. Fox, and M. W. Ratner, "Nonlinear Optimization Using the Generalized Reduced Gradient Method," *RAIRO Operations Research*, Vol. 8, Issue V3, 1974, pp. 73–103.

#### VIII. BIOGRAPHIES

Anirudhh Ravi is a power engineer at Schweitzer Engineering Laboratories, Inc. (SEL). He earned his Bachelor of Technology (BTech) degree in electrical and electronics engineering from SRM Institute of Science and Technology,

Chennai, India, in 2019 and received his MS in electrical engineering from North Carolina State University at Raleigh in 2021. Anirudhh joined SEL as an associate power engineer in the Research and Development division in 2022 and is currently working as a power engineer.

Veselin Skendzic is a fellow engineer at Schweitzer Engineering Laboratories, Inc. (SEL). He earned his BS in electrical engineering from FESB, University of Split, Croatia; his MSc from ETF, Zagreb, Croatia; and his PhD from Texas A&M University. He has more than 30 years of experience in electronic circuit design and power system protection-related problems. He is an IEEE Fellow, has written multiple technical papers, has over 20 patents, and is actively contributing to IEEE and IEC standard development.

Vinod Yedidi is a senior engineer in the Research and Development division of Schweitzer Engineering Laboratories, Inc. (SEL). He has been with the company since 2006. Vinod received his MS in electrical engineering from University of Idaho in 2006 and his BS in electrical and electronics engineering from the Jawaharlal Nehru Technological University College of Engineering in Hyderabad, India, in 2002. He has been a member of IEEE for 25 years and is a registered professional engineer in Washington.

Colby Clark received his BS in electrical and computer engineering from Rowan University, New Jersey, in 2020. He joined Schweitzer Engineering Laboratories, Inc. (SEL) in 2022 as an associate hardware engineer working for their Research and Development division.

**Balaji Janarthanan** is a senior engineering manager at Schweitzer Engineering Laboratories, Inc. (SEL). He earned his Bachelor of Engineering degree in Electronic & Communication Engineering from Government College of Technology, Coimbatore, India, and received his Master of Science degree in Software Systems from The Birla Institute of Technology & Science from Pilani, India. He joined SEL in 2008 and works in firmware development of protective relays.